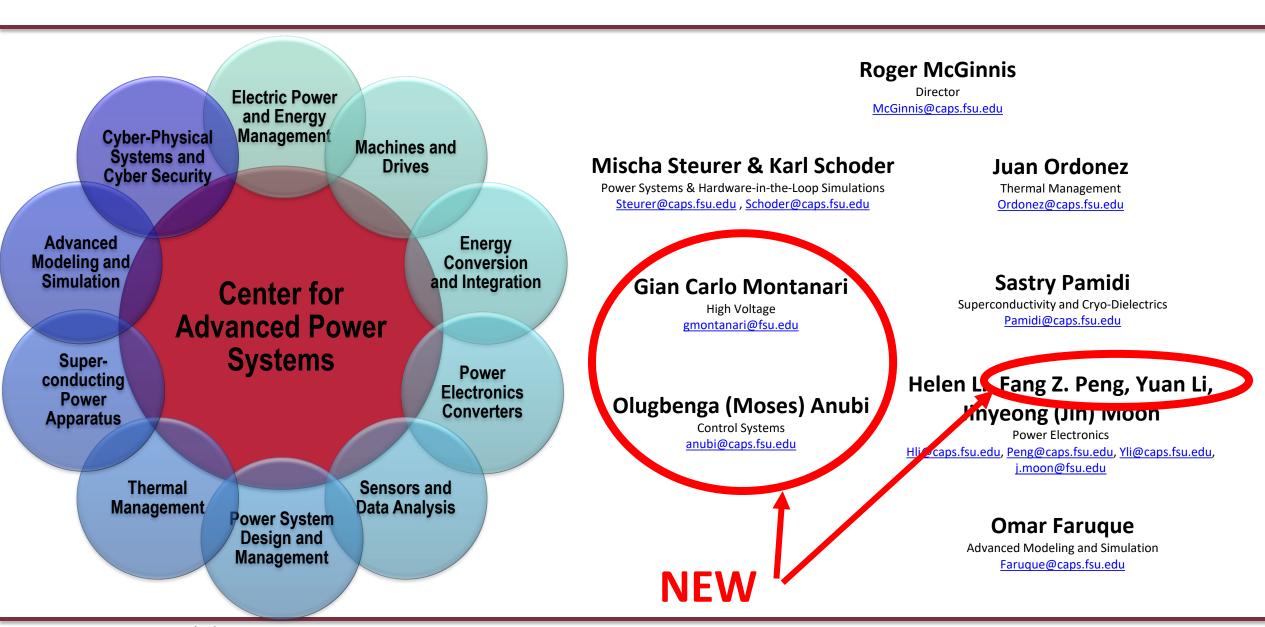

# Florida State University Center for Advanced Power Systems

Michael "Mischa" Steurer

Power Systems Group Lead, Steurer@caps.fsu.edu

**NEW**

#### Research Areas and Contacts

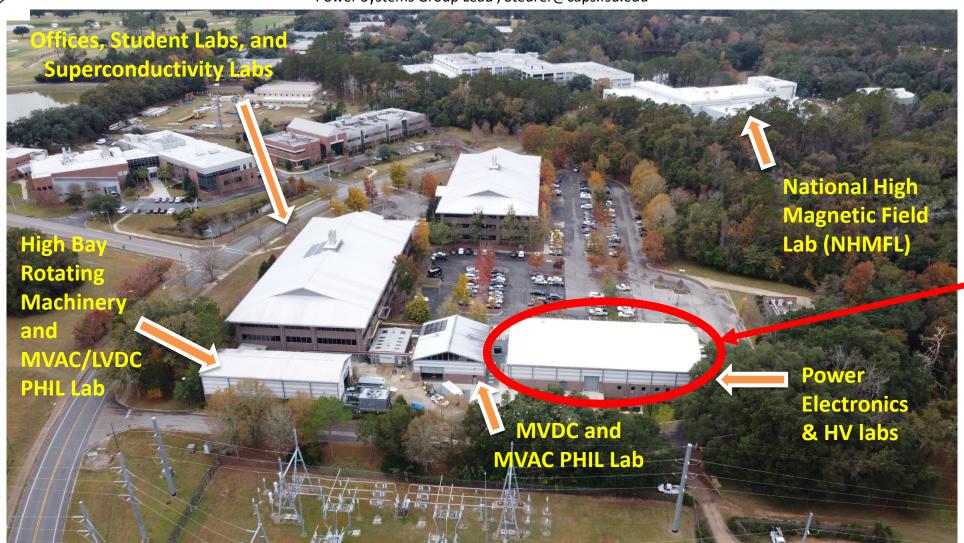

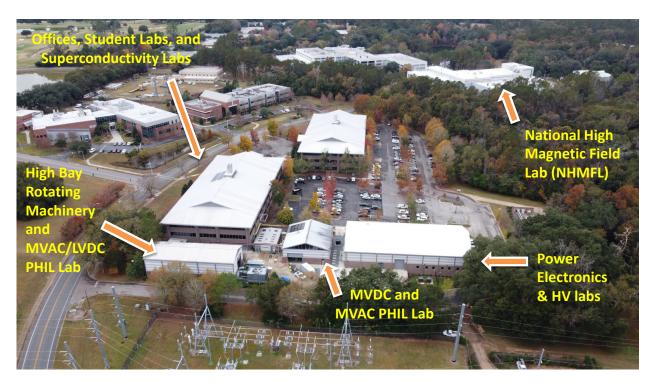

## FSU Center for Advanced Power Systems - CAPS

- Research and education related to application of new technologies to electric power systems

- Closely affiliated with FAMU-FSU

College of Engineering

- 56,000 ft<sup>2</sup> laboratories/offices;

CUI data security compliant

- Tenure/Non-tenure track faculty, Ph.D./M.S./B.S. students, staff researchers and post-doctorial associates and facility support

- Over **\$45** million specialized power and energy capabilities funded by ONR, DOE, NSF and Industry

- Lead university of the ONR funded Electric Ship Research and Development Consortium (ESRDC)

- Contracted by NAVSEA-PMS460 to conduct HIL based demonstrations of advanced P&E technologies

- Also funded from DOE-EERE, ARPA-E, and **industry partners** (e.g. STTR/SBIR, others)

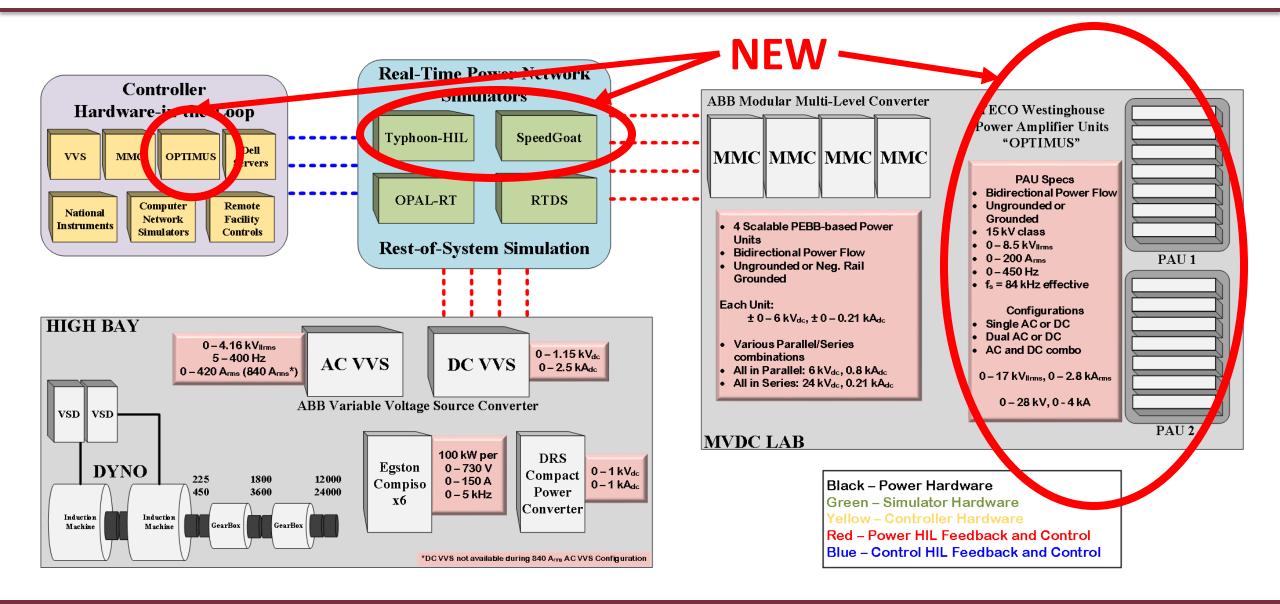

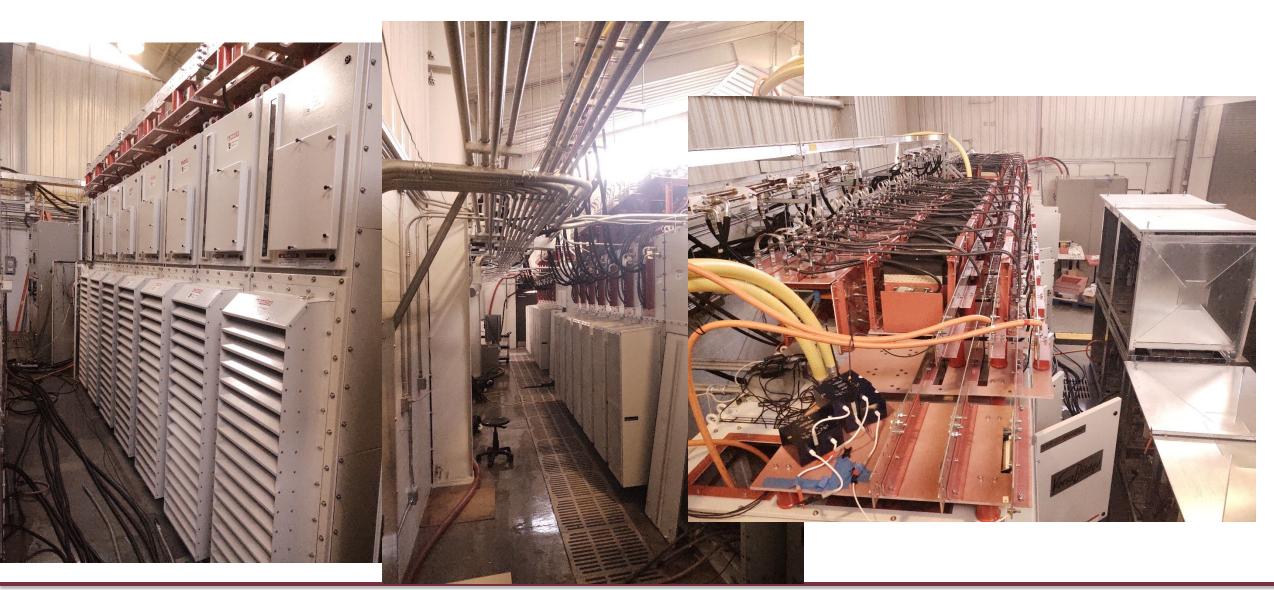

#### **FSU-CAPS 5 MW Facilities**

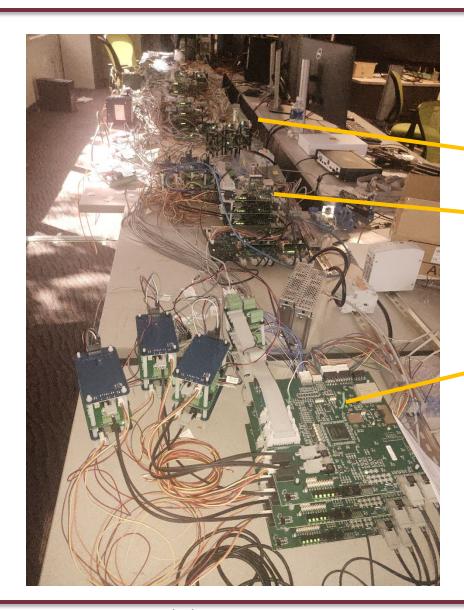

#### **NEW** – RT Simulator Upgrades

# 8 new RTDS NovaCor systems totaling 8 fully loaded NovaCor chassis

- IBM Power 8 processors (10 cores/ processor)

- 3 PB5 (processor) racks also present

- Additions enable

- Simulations with 4,800 nodes

- Multi-rate simulation capable

- Improved CHIL performance (e.g., MMC CHIL)

## **NEW** – RT Simulator Upgrades

#### 2 SpeedGoat Performance Real-Time Target Machines

- Dedicated hardware for running MathWorks Simulink models in real-time

- Tandem operation with other simulators and controllers for PHIL and CHIL testing

- Intel Core i7 4.2 GHz 4 core processor

- Integrated FPGA modules for low-timestep simulations and high-speed communication

# 2 Typhoon HIL404 RTS

- Four cores/system, can be paralleled for larger simulations

- 96 analog and digital I/O

- Simulation timesteps as low as 200ns for low-latency simulations (e.g., buck/boost converter)

#### **NEW** – RT Simulator Upgrades

# Opal-RT Real-Time Target Machines

- CPU and high-end reconfigurable FPGA

- 256 I/O lines and 16 high-speed SFP ports

- CPU time step  $\geq$  20  $\mu$ s

- FPGA-based Power Electronics Tool box (eHS128) supports up to 144 switches and 344 states, with time step as low as 210 ns

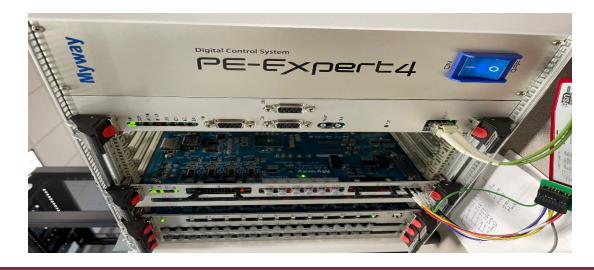

#### **PE Expert**

- Digital platform for advanced power electronics

- TI6657 DSP + FPGA architecture enables high-speed control system, over 300 kHz carrier frequency

- Over 144 PWM control and sensor inputs

- PSIM SimCoder PE-Expert4 target option enabling advanced RCP (Rapid Control Prototyping)

- Automation and run-time debugging with full visibility of inside of the control

# TEC Westinghouse

2 x Power Amplifier Units (PAUs) in CAPS MVDC Lab

In: 600V AC, 3-ph, 60 Hz

Out: 0....800 Vrms 1-ph

Slice

#### 15 kV class

$0....8.5 \text{ kV}_{rms} \text{ L-L} \\ 0...200 \text{ A}_{rms}$

#### 0...450 Hz

Bi-directional power flow

$f_S = 7*12 = 84 \text{ kHz}$

4.16 kV utility feed

FSU-CAPS Update 11/9/2022

8

grounded or ungrounded

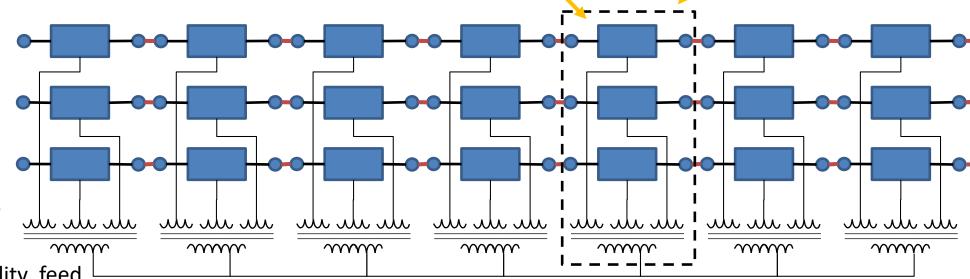

## **NEW** – Reconfigurable MW Class PHIL Amplifier

#### **NEW** – Inter-Lab Connectivity and Cooling Capacity

2 x 5 MW connection between MVDC lab and high bay

**70 Ton Chiller**

## NEW – CHIL of Reconfigurable MW Class PHIL Amplifier