# Performance and Reliability of Bonded Interfaces for High-Temperature Packaging

# **Annual Report**

Douglas DeVoto

NREL is a national laboratory of the U.S. Department of Energy Office of Energy Efficiency & Renewable Energy Operated by the Alliance for Sustainable Energy, LLC

This report is available at no cost from the National Renewable Energy Laboratory (NREL) at www.nrel.gov/publications.

Management Report NREL/MP-5400-64942 April 2016

Contract No. DE-AC36-08GO28308

# Performance and Reliability of Bonded Interfaces for High-Temperature Packaging

# **Annual Report**

Douglas DeVoto

Prepared under Task No. VTP2.7201

NREL is a national laboratory of the U.S. Department of Energy Office of Energy Efficiency & Renewable Energy Operated by the Alliance for Sustainable Energy, LLC

This report is available at no cost from the National Renewable Energy Laboratory (NREL) at www.nrel.gov/publications.

National Renewable Energy Laboratory 15013 Denver West Parkway Golden, CO 80401 303-275-3000 • www.nrel.gov Management Report NREL/MP-5400-64942 April 2016

Contract No. DE-AC36-08GO28308

#### NOTICE

This report was prepared as an account of work sponsored by an agency of the United States government. Neither the United States government nor any agency thereof, nor any of their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States government or any agency thereof.

Cover Photos by Dennis Schroeder: (left to right) NREL 26173, NREL 18302, NREL 19758, NREL 29642, NREL 19795.

NREL prints on paper that contains recycled content.

# I.1. Performance and Reliability of Bonded Interfaces for High-Temperature Packaging

#### **Principal Investigator: Douglas DeVoto**

National Renewable Energy Laboratory (NREL) 15013 Denver West Parkway Golden, CO 80401 Phone: 303-275-4256 E-mail: douglas.devoto@nrel.gov

#### DOE Technology Development Manager: Susan A. Rogers

U.S. Department of Energy 1000 Independence Ave. SW EE-3V Washington, DC 20585 Phone: 202-586-8997 E-mail: susan.rogers@ee.doe.gov

#### NREL Task Leader: Sreekant Narumanchi

Phone: 303-275-4062 Email: sreekant.narumanchi@nrel.gov

#### **Abstract/Executive Summary**

Current generation automotive power electronics packages utilize silicon devices and lead-free solder alloys. To meet stringent technical targets for 2020 and beyond (for cost, power density, specific power, efficiency and reliability), wide-bandgap devices are being considered since they offer advantages such as operation at higher frequencies, voltages, and temperatures. Traditional power electronics packages must be redesigned to utilize the full potential of wide-bandgap devices, and the die- and substrate-attach layers are key areas where new material development and validation is required. Present solder alloys do not meet the performance requirements for these new package designs while also meeting cost and hazardous substance restrictions.

Sintered silver (Ag) promises to meet the needs for die- and substrate-attach interfaces but synthesis optimization and reliability evaluation must be completed. Sintered Ag material was proposed as an alternative solution in power electronics packages almost 20 years back. However, synthesis pressure requirements up 40 MPa caused a higher complexity in the production process and more stringent flatness specifications for the substrates. Recently, several manufacturers have developed sintered Ag materials that require lower (3 - 5 MPa) or even no bonding pressures.

Degradation mechanisms for these sintered Ag materials are not well known and need to be addressed. We are addressing these aspects to some extent in this project. We are developing generalized (i.e., independent of geometry) stress intensity factor versus cycles-to-failure relations for sintered Ag. Because sintered Ag is a relatively new material for automotive power electronics, the industry currently does not have a good understanding of recommended synthesis parameters or expected reliability under prescribed conditions. It is an important deliverable of this project to transfer findings to industry to eliminate barriers to using sintered Ag as a viable and commercialized die- and substrate-attach material. Only a few manufacturers produce sintered Ag pastes and may consider some processing conditions as proprietary. It is the goal of this project to openly explore and define best practices in order to impact the maximum number of power electronics module manufacturers and suppliers.

#### Accomplishments

• Established and initiated a procedure for the material and degradation characterization of sintered Ag through long-term accelerated temperature testing.

- Processed coefficient of thermal expansion (CTE)-mismatched disk samples with various diameter bond pads to validate stress field relationship with delamination initiation. Monitored delamination rates through acoustic microscopy while samples were subjected to accelerated temperature testing.

- Synthesized and shear tested initial samples for mechanical characterization of sintered Ag. Material properties gathered are replacing bulk silver material properties to more accurately model the interface structure.

$\diamond \quad \diamond \quad \diamond \quad \diamond \quad \diamond \quad \diamond$

#### Introduction

Standard packaging technologies have limited the advancement of automotive power electronics modules toward designs that promise higher performance and reliability. The drive toward reduced cost, weight, and volume of components in electric-drive vehicles has led to increased performance demands on power electronics modules. Increased power densities and larger temperature extremes reduce lifetimes for traditional power electronics packages and require new materials and manufacturing processes to be utilized. Before new technologies can be introduced into commercial products, their reliability must be evaluated and quantified.

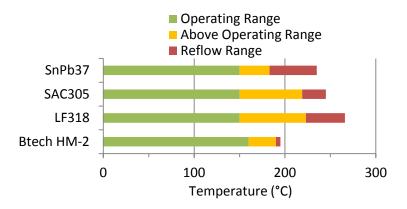

Current power electronics packages utilize silicon devices and lead-free solder alloys within their construction. As package designs transition to wide-bandgap devices, interface materials must improve to fully utilize the capabilities of these new devices [1-5]. Current solder alloys exhibit creep effects when subjected to elevated temperatures and cannot operate at temperatures as high as 200°C. The operating ranges of several currently used interface materials are shown in Figure 1.

Figure 1: Operating range of common interface materials

Research efforts for high-temperature bonded interface materials can be roughly classified into three categories: Ag sintering, high-temperature soldering, and transient liquid phase (TLP) sintering. The advantages and disadvantages to these processing technologies are summarized in the Table 1.

#### Table 1: Emerging Die- and Substrate-Attach Processes.

| Process                    | Advantages                                               | Disadvantages                                                              |  |  |

|----------------------------|----------------------------------------------------------|----------------------------------------------------------------------------|--|--|

| Ag sintering               | High thermal conductivity, highest operating temperature | High processing pressure, material cost                                    |  |  |

| High-temperature soldering | Similar to current soldering procedures                  | High processing temperature,<br>higher residual stresses, material<br>cost |  |  |

| TLP sintering              | Minimal bonding pressure                                 | Processing time, navigating phase diagrams                                 |  |  |

Some solder alloys have been developed for high-temperature operation, but face cost limitations (e.g., gold alloys) or do not meet Restriction of Hazardous Substances standards (e.g., high-lead alloys). Additionally, solder alloys must always be processed at temperatures higher than their desired operating temperature because their reflow temperatures are equivalent to their processing temperature. This imparts higher residual stresses onto the devices and insulating substrates during processing. Some power electronics module suppliers are evaluating high-temperature solders as a "drop-in" replacement to previously used solder alloys and acknowledge the higher associated material costs.

TLP sintering involves an assembly or paste of low- and high-melt materials. Processing occurs at low temperatures  $(250^{\circ}\text{C} - 300^{\circ}\text{C})$  where the low-melt component material diffuses into the high-melt material to form intermetallic compounds. These intermetallic compounds will only re-melt at temperatures much higher than the processing conditions  $(400^{\circ}\text{C} - 600^{\circ}\text{C})$ . Toyota Research Institute of North America has several publications on the development of nickel-tin (Ni-Sn) TLP bonding for automotive power electronics. The University of Maryland's Center for Advanced Life Cycle Engineering is working to develop Ni-Sn and copper-tin (Cu-Sn) TLP bonding systems while Ames Laboratory has developed a Cu-Ni TLP process.

Sintered Ag material has been proposed as an alternative solution in power electronics packages as far back as 20 years. To reduce synthesis temperatures to below 300°C, the concurrent application of pressure up to 40 MPa onto the package or sintered Ag bonded interface material (BIM) was originally advocated. However, this caused a higher complexity in the production process and more stringent flatness specifications for the substrates. Recently, several manufacturers have developed sintered Ag materials that require lower (3 – 5 MPa) or even no bonding pressures. Virginia Tech, Heraeus, Henkel, and Kyocera have developed these materials. Semikron currently has production power electronics utilizing sintered Ag as the die-attach layer. Large-area substrate attachment requires additional research and development for power electronics module suppliers to transition to sintered Ag. Prior work at NREL and Oak Ridge National Laboratory (ORNL) has demonstrated the promise of the processing technology, but a comprehensive evaluation of all processing variables is needed to demonstrate best practices to industry.

#### Approach

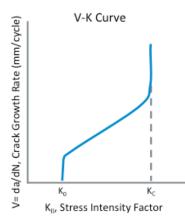

Conventional high-temperature bonded interfaces within the power electronics module face CTE mismatches between materials/layers and resultant thermomechanical stresses. This can cause formations of voids and cracks in these bonded interfaces as well as delaminations, which pose a problem from a reliability standpoint. These defects manifest themselves in increased thermal resistance in the package, acting as a bottleneck to heat removal from the package. Research at NREL and ORNL has focused on evaluating the reliability of low- and no-pressure sintered Ag interface pastes. Prior samples have established a failure behavior that is consistent with stress-corrosion (fatigue) cracking. The experimental observation of cohesive failure of the sintered Ag interconnection allows us to combine the tracked ingress front of the delamination (captured with acoustic imaging) with their modeled thermomechanical strains and stress concentrations (also linked to the size and shape of the interconnection at any given time instant) to construct and interpret a crack velocity (V)-stress field (K) parameter response, or V-K curve, of a particular sintered Ag material, as shown in Figure 2.

Figure 2: V-K curve

While the authors recognize this study's interpretation may be specific to the employed sintered Ag paste, the authors feel the analysis method may provide a logical way to interpret such damage in interconnections of any no-pressure sintered Ag paste.

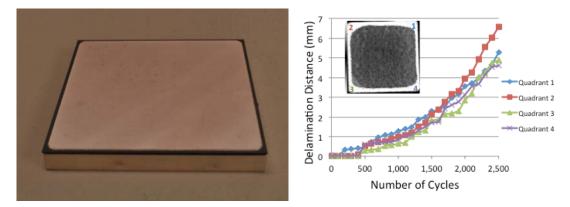

A description of the experiment, finite element modeling of the thermomechanical strains and stress concentrations, the construction of a V-K curve using the data and its interpretation will be presented. Crack growth rates within the sintered Ag BIM were determined as a function of number of thermal cycles from past work [6]. The assembly consisted of a 5-mm-thick Cu base plate attached to a 0.72-mm-thick active metal bonded substrate (0.32-mm-thick silicon nitride [Si<sub>3</sub>N<sub>4</sub>] with 0.2-mm-thick Cu foil on either side of Si<sub>3</sub>N<sub>4</sub>, 50.8  $mm \times 50.8$  mm cross-sectional area footprint) via the bonding material. The Cu metallization layers were inset 1 mm from the perimeter of the Si<sub>3</sub>N<sub>4</sub>, for a 48.8 mm × 48.8 mm footprint, and the corners were given a radius of 2 mm to minimize stress intensities. Before assembly, the Cu metallization layers in the substrate were plated with 4 µm of electroless Ni-P, 1 µm of Pd, and 0.3 µm of Ag to improve adhesion with the bonding material. The Cu base plate was electroplated with 5 µm of Ag. Bonded interfaces based on sintered-silver particles were synthesized by Semikron (Nürnberg, Germany). Corners of the Si<sub>3</sub>N<sub>4</sub> substrate were rounded off to match the 2-mm radius of the Cu metallization layers. The sample assembly was placed in a hot press and raised to its processing temperature, after which pressure was applied. Semikron did not provide specifics of the sintering temperature and schedule and bonding pressure. Three characteristic regions of the delamination distance were observed, where the delamination distance from the original corner in each quadrant for a sample is shown in Figure 3. No delamination occurred within the first few hundred cycles in any of the samples. Immediately after initiation, a region of transient increase in delaminated distance then occurred for the next few hundred cycles. Lastly, a constant or increasing rate of delamination distance occurred for the remainder of the testing. The observation of three such regions is consistent with those observed with the damage tolerant criterion (da/dN vs. K or  $\Delta$ K) for fatigue whose crack initiation and growth behavior follows a classic brittle fracture mechanics pattern.

Figure 3: Representative metalized substrate/base plate assembly for sintered-silver (left) and delamination distance of sintered Ag BIM as a function of number of thermal cycles, or da/dN curves (right)

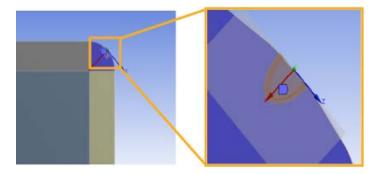

The main objective of the computational modeling approach in this work is to calculate the values of the stress field parameter using finite element analysis at various points along crack growth in sintered Ag BIMs. The 50-mm × 50-mm sample shown in Figure 3 was selected for modeling as the C-mode scanning acoustic microscope (C-SAM) images of the sintered Ag interface within the sample were already available. The stress field parameter chosen for this study is the J-integral (mJ/mm<sup>2</sup>), which is a theoretical parameter whose magnitude determines the intensity of stresses in the crack tip region. It depends on the sample geometry, size, location of the crack, and magnitude and distribution of the load. J-integral, a contour integral, is a single-parameter characterization of the crack tip stress field. The value of J-integral around a crack tip is independent of the path of integration. Once computed, J-integral values will be correlated with the crack velocities calculated from C-SAM images of delaminated sintered Ag. A three-dimensional elastic-plastic fracture mechanics-based crack initiation and propagation model of the sample shown in Figure 3 with sintered Ag interface is being developed to obtain the desired outputs. The insertion of a crack feature at the far corner region within the sintered Ag interface within ANSYS is shown in Figure 4. Analysis of the resulting J-integral describes the stress field near a crack tip for inelastic deformation.

#### Figure 4: Crack inserted into the sintered Ag layer

An identified V-K curve is important because it affords the possibility to pre-determine what sizes and shapes of sintered Ag interconnects can be used without causing delamination, which has positive implications for future reliability improvement with power electronic devices.

#### **Results and Discussion**

#### **Synthesis**

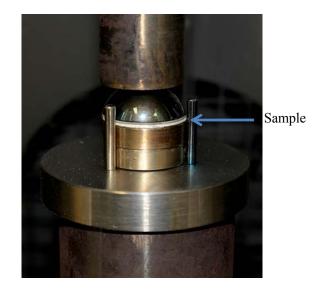

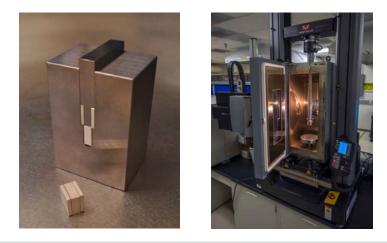

Test samples used for evaluation at NREL were synthesized at ORNL. Coupons that were 25.4 mm in diameter and 2 mm in thickness were first machined from Invar and Cu. The two materials were selected for their CTE mismatch, with Cu having a CTE of 16.5 (ppm/°C) and Invar having a CTE of 1.3-2.7 (ppm/°C). Surfaces were Blanchard ground and then metalized with Ag. Coupon materials were matched in several configurations, Cu to Cu, Invar to Invar, and Cu to Invar. Stencil patterns of 10 mm, 18 mm, and 22 mm diameters were centered over one test coupon, and one print of Henkel paste was applied. After drying in a nitrogen environment at 100°C for two hours, the top metal coupon was placed above the dried Ag paste, and the sample assembly was placed within the sintering fixture, as shown in Figure 5.

#### Figure 5: Sample sintering assembly

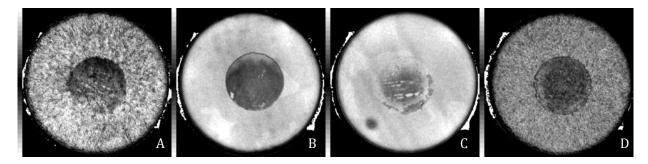

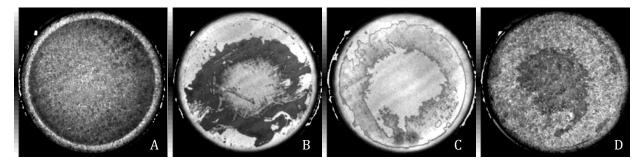

Pressure was applied to the sintering assembly and the temperature was raised to 250°C. After the sample was allowed to cool, the interface was inspected via acoustic microscopy. Samples from Cu-Cu, Invar-Invar, and Cu-Invar coupons with 10-mm diameter stencils are shown in Figure 6.

Cu-Cu coupons exhibited some defects after sintering that prevented a complete 10-mm diameter bond area. The partial delamination observed in some samples likely occurred during the cool-down phase to room temperature after sintering. Artifacts from scanning through 2 mm of Cu are present and should be disregarded. Invar-Invar coupons exhibited good initial adhesion with a clear bond edge. For Cu-Invar samples, the Cu coupon was used for drying the Ag paste while the Invar coupon was placed on top prior to sintering. The Invar coupons exhibited poor adhesion to the sintered Ag layer in this sample configuration, as shown by lighter areas within the 10-mm bond pad region. An additional set of Invar-Invar samples were sintered for a longer duration of two hours instead of one and were included in this reliably study.

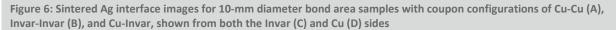

The quality of the sintered Ag bond pad was also analyzed for 18-mm diameter bond pad samples, shown in Figure 7.

Figure 7: Sintered Ag interface images for 18-mm diameter bond area samples with coupon configurations of Cu-Cu (A), Invar-Invar (B), and Cu-Invar, shown from both Invar (C) and Cu (D) sides

Cu-Cu and Invar-Invar samples both exhibited quality adhesion between the interface material and the coupons. Cu-Invar coupons did not achieve a quality bond as the Invar coupon had poor adhesion within the central area of the bond pad and the Cu coupon showed delamination around the perimeter of the bond pad. The lower quality of the Cu-Invar coupons can be attributed to the CTE mismatch within the samples. While sintered Ag and Cu share close CTE values, the mismatch with Invar intentionally creates stress within the sample package. Values of the materials are shown in Table 2.

| Material    | CTE<br>(ppm/°C) | E<br>(GPa) |

|-------------|-----------------|------------|

| Cu          | 17              | 115        |

| Sintered Ag | 20              | 15 - 60    |

| Invar       | 1.3 – 2.7       | 145        |

### **Table 2: Material Properties**

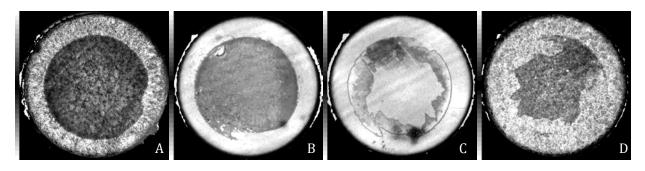

Acoustic images were also evaluated for 22-mm-diameter bond pad samples, shown in Figure 8.

Figure 8: Sintered Ag interface images for 22-mm diameter bond area samples with coupon configurations of Cu-Cu (A), Invar-Invar (B), and Cu-Invar, shown from both Invar (C) and Cu (D) sides

Cu-Cu samples exhibited uniform adhesion between the coupons and the sintered Ag interface. Invar-Invar samples had difficulty maintaining a bond pad to the perimeter of the 22-mm diameter stencil. Cu-Invar samples again showed delamination after the sintering process due to the CTE mismatch. The Cu coupon maintained adhesion within its middle while the Invar coupon only had adhesion around the perimeter.

#### **Accelerated Testing**

The bonded samples were subjected to temperature cycling conditions from -40°C to 170°C at ramp rates of 5°C/min and dwell periods of 15 minutes. Samples were removed from the environmental test chamber every 100 cycles, and the sintered Ag interface was reexamined from both coupon sides. No visual changes were observed in the acoustic images to indicate degradation of the sintered Ag layer; however, coupons were found

to have fully separated after several hundred thermal cycles. Table 3 summarizes the bond condition of all samples; green indicates a bonded sample, and red indicates that separation occurred after the previous scan and before the current scan interval. As an example, Sample 5 passed the initial acoustic scan with no apparent defects but was found to have delaminated after it was inspected at 100 cycles. Please note that samples 10–12 were a second set of Invar-Invar samples that were sintered for a longer duration than other samples.

| Sample |             | Stencil<br>Diameter<br>(mm) | Cycles |     |     |     |     |     |

|--------|-------------|-----------------------------|--------|-----|-----|-----|-----|-----|

| Number |             |                             | 0      | 100 | 200 | 300 | 400 | 500 |

| 1      | Cu-Cu       | 10                          |        |     |     |     |     |     |

| 2      | Cu-Cu       | 10                          |        |     |     |     |     |     |

| 3      | Cu-Cu       | 10                          |        |     |     |     |     |     |

| 4      | Invar-Invar | 10                          |        |     |     |     |     |     |

| 5      | Invar-Invar | 10                          |        |     |     |     |     |     |

| 6      | Invar-Invar | 10                          |        |     |     |     |     |     |

| 7      | Cu-Invar    | 10                          |        |     |     |     |     |     |

| 8      | Cu-Invar    | 10                          |        |     |     |     |     |     |

| 9      | Cu-Invar    | 10                          |        |     |     |     |     |     |

| 10     | Invar-Invar | 10                          |        |     |     |     |     |     |

| 11     | Invar-Invar | 10                          |        |     |     |     |     |     |

| 12     | Invar-Invar | 10                          |        |     |     |     |     |     |

| 13     | Cu-Cu       | 18                          |        |     |     |     |     |     |

| 14     | Cu-Cu       | 18                          |        |     |     |     |     |     |

| 15     | Cu-Cu       | 18                          |        |     |     |     |     |     |

| 16     | Invar-Invar | 18                          |        |     |     |     |     |     |

| 17     | Invar-Invar | 18                          |        |     |     |     |     |     |

| 18     | Invar-Invar | 18                          |        |     |     |     |     |     |

| 19     | Cu-Invar    | 18                          |        |     |     |     |     |     |

| 20     | Cu-Invar    | 18                          |        |     |     |     |     |     |

| 21     | Cu-Invar    | 18                          |        |     |     |     |     |     |

| 22     | Cu-Cu       | 22                          |        |     |     |     |     |     |

| 23     | Cu-Cu       | 22                          |        |     |     |     |     |     |

## **Table 3: Failure Rate of Test Samples**

.

| 24 | Cu-Cu       | 22 |  |  |  |

|----|-------------|----|--|--|--|

| 25 | Invar-Invar | 22 |  |  |  |

| 26 | Invar-Invar | 22 |  |  |  |

| 27 | Invar-Invar | 22 |  |  |  |

| 28 | Cu-Invar    | 22 |  |  |  |

| 29 | Cu-Invar    | 22 |  |  |  |

| 30 | Cu-Invar    | 22 |  |  |  |

As the initial acoustic images indicated, the poor bonding of the Cu-Invar samples due to the intended CTE mismatch quickly led to separation of the test coupons. This was consistently shown for 10-, 18-, and 22-mm bond pad diameter samples, with no samples reaching 500 cycles. Several Invar-Invar samples also failed, with two of the three failures occurring in the samples that were sintered for a longer duration. Samples will continue to be cycled until all samples reach failure, presently defined as complete separation of the coupons from each other.

### **Mechanical Testing**

While the mechanical properties of bulk Ag are well known, variations in paste manufacturer, drying procedure, and sintering method can all lead to significant differences in properties for sintered Ag. To obtain the needed material properties for accurate modeling of the interface, shear testing of the material was completed. Three Cu coupons comprise the shear test sample, all 12.7 mm  $\times$  12.7 square. The middle coupon is 5 mm thick while the outer coupons are 1.8 mm thick. The desired bonded interface material is used to adhere the three coupons together into a test sample. This sample is placed in a shear test fixture that supports the outer coupons while applying a load to the middle coupon. The symmetry of the test samples allows for the interface layers to be loaded in a pure shear fashion. A test sample and the shear fixture are shown in Figure 9. The shear fixture is placed within an Instron 5966 dual column testing system that can be configured with 100 N and 10 kN load cells. The environmental chamber has a temperature range from -100°C to 350°C for capturing temperature-dependent material properties. A noncontact video extensometer is used for strain measurements. The Instron mechanical testing system is shown in Figure 9.

Figure 9: Test sample and shear test fixture (left) and Instron mechanical testing system (right)

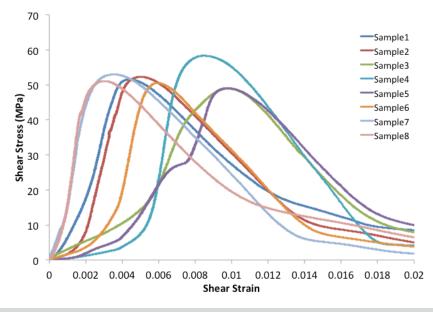

To validate the shear testing procedure,  $Sn_{63}Pb_{37}$  solder was used to synthesize several samples. Solder preforms were placed between the test coupons along with a few glass beads to ensure planarity of the bond line. After a solder reflow process was completed, the bond layers were inspected by acoustic microscopy. Only samples with minimal voiding were selected for shear testing. After screening, samples were placed within the shear test fixture and sheared at a strain rate of 0.02. The video extensometer measured displacement change of the fixture and the testing system recorded the compressive loading. Shear stress was calculated by dividing the compressive loading force by the bonded area of the test coupons. The acoustic images revised the bonded area by subtracting voided areas. A compilation of stress-strain curves of  $Sn_{63}Pb_{37}$  solder samples is shown in Figure 10.

Figure 10: Solder stress-strain curves

The maximum shear stress and shear modulus of the test samples were compared to values found in literature. A shear stress of 50.5 MPa and a shear modulus of 12.2 GPa compare favorably to values reported by Darveaux [7].

| Source       | Shear Stress<br>(MPa) | Shear Modulus<br>(GPa) |

|--------------|-----------------------|------------------------|

| NREL         | 50.5                  | 12.2                   |

| Darveaux [7] | 50.5                  | 13.1                   |

## Table 4: Shear Stress and Shear Modulus Comparison

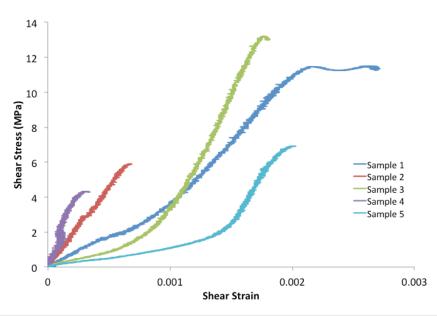

The shear testing procedure was repeated with sintered Ag samples. Stress-strain curves are shown in Figure 11.

Figure 11: Sintered Ag stress-strain curves

When compared to previous Sn<sub>63</sub>Pb<sub>37</sub> solder samples, it was found that sintered Ag samples reached their ultimate strength with very little displacement, confirming that creep effects are minimal within the material. Variation in ultimate strength varied more from sample to sample and may be contributed to synthesis variations between samples. The maximum shear stress values are also significantly lower than measurements of Sn<sub>63</sub>Pb<sub>37</sub> solder samples indicating that additional synthesis optimization is required.

#### **Crack Modeling**

Previously, the objective of the computational modeling approach in this work was to obtain stress intensity factor (K) values using finite element analysis at various points along crack growth in sintered Ag BIMs. Stress intensity factor was chosen as the fracture mechanics parameter as it was assumed that sintered Ag BIM was elastic under the given thermal loading condition. However, further literature review revealed the occurrence of ductile fracture [8] in which plastic deformation is the dominant failure mechanism. In such a case, an elastic-plastic fracture mechanics analysis is in order, and parameters such as J-integral, which characterizes the stress and strain fields around a crack tip in a plastic material, need to be computed. J-integral is defined as a path-independent contour integral around a crack tip and is equal to the nonlinear energy release rate.

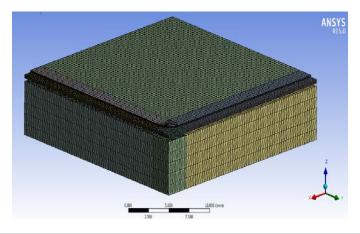

The 50-mm  $\times$  50-mm sample shown in Figure 12 was selected for modeling as the C-SAM images of the sintered Ag interface within the sample were already available. J-integral values, once computed, will be correlated with the crack velocities or crack length calculated from C-SAM images of the delaminated sintered Ag. The crack-modeling feature in ANSYS is only available in version 15 or later. Crack size and location need to be known before an analysis can be completed. The sample geometry was created in ANSYS Design

Modeler, and a tetrahedral mesh was implemented. While a hexahedral mesh would provide more accurate results, the current capabilities within ANSYS are limited to performing crack modeling on a tetrahedral mesh.

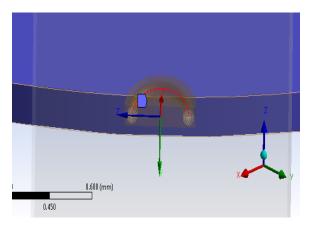

Figure 12: Quarter symmetry tetrahedral mesh of the 50 x 50-mm sample

A crack was then inserted at the far corner region within sintered Ag using the "Fracture" feature available in ANSYS Model, shown in Figure 13. The crack takes a semi-elliptical shape, and the major and minor radii are defined to create a crack of the desired size. Currently, only a semi-elliptical shaped crack is available in ANSYS. After solving, J-integral values can be obtained along the crack contour in the post-processing phase. If the maximum value of the J-integral exceeds a critical value, which is unique for each material, it can be understood that crack would begin to propagate. However, crack propagation modeling is not currently available within ANSYS.

Figure 13: Crack inserted into the sintered Ag layer

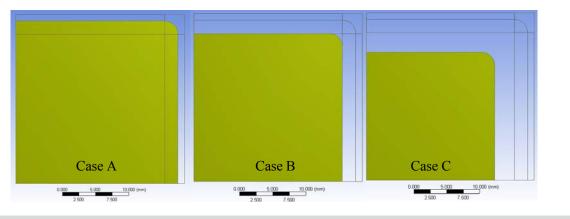

To simulate crack propagation or crack growth, multiple simulations with reduced bonded areas were conducted, as shown in Figure 14. Currently, the reduction in bonded areas was chosen arbitrarily to analyze the variation in J-integral values along crack growth path. Preliminary J-integral results have been obtained from these simulations. Additional work such as mesh independence study is being conducted to confirm the validity of the obtained results.

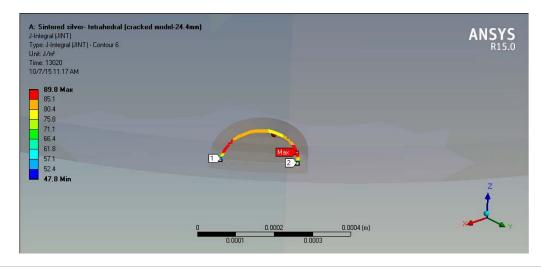

Three different simulations with varying bonded areas were conducted. The crack feature in ANSYS was modeled in all three simulations, and J-integral values were obtained. The maximum value of the J-integral obtained along the crack contour was selected as the main output, as shown in Figure 15.

Figure 15: J-Integral contour plot

The obtained values of the J-integral along the crack contour are compiled in Table 5.

#### **Table 5: J-integral from Three Simulations**

| Case | J-Integral<br>(J/m <sup>2</sup> ) |

|------|-----------------------------------|

| А    | 89.8                              |

| В    | 129.2                             |

| С    | 160.5                             |

These preliminary results show an increasing trend in the J-integral value around the crack tip as crack growth occurs. More simulations with reduced bonded areas need to be conducted to capture a detailed trend.

#### **Conclusions and Future Directions**

As maximum device temperatures approach 200°C continuous operation, sintered Ag materials promise to maintain bonds at these high temperatures without excessive degradation rates. Working in close collaboration

with ORNL, a detailed characterization of the thermal performance and reliability of sintered Ag materials and processes has been initiated. The CTE mismatch within Cu-Invar samples quickly led to separation of the test coupons. This was consistently shown for 10-, 18-, and 22-mm bond pad diameter samples, with no samples reaching 500 cycles. When compared to Sn<sub>63</sub>Pb<sub>37</sub> solder samples, it was found that sintered Ag samples reached their ultimate strength with very little displacement. ORNL and NREL will continue to optimize the synthesis process for sintered Ag and will continue to provide the automotive industry a baseline for the reliability of these interfaces.

Future steps in crack modeling include efforts to simulate crack propagation directly using the extended finite element method (X-FEM). X-FEM is a numerical technique that uses partition of unity method for modeling discontinuities such as cracks in a system. The biggest advantage of XFEM is that crack propagation can be modeled without re-meshing. Also, we will investigate the application of cohesive zone models, which employ traction-separation laws, in an X-FEM framework to simulate cohesive crack growth.

Development of lifetime estimation tools will allow the reliability of sintered Ag to be predicted (similar to the reliability prediction of solder materials), and enable a time and cost-effective design process. Performance and reliability of novel/emerging techniques such as atomic-level bonding (in collaboration with industry) will also be investigated as a longer-term development goal.

#### FY 2015 Presentations/ Publications/ Patents

- 1. D.J. DeVoto, A.A. Wereszczak, and P.P. Paret. 2015. "Thermomechanical Reliability of Sintered-Silver Interface Materials." International Technical Conference and Exhibition on Packaging and Integration of Electronic and Photonic Microsystems (InterPACK), San Francisco, CA.

- 2. A.A. Wereszczak, S.B. Waters, D.J. DeVoto, and P.P. Paret. 2015. "Method to Determine Maximum Allowable Sinterable Silver Interconnect Size." In preparation, Journal of Electronic Materials.

- D.J. DeVoto. 2015. "Performance and Reliability of Bonded Interfaces for High-Temperature Packaging." Electric Drive Technologies (EDT) Program FY15 Annual Merit Review, DOE Vehicle Technologies Office, Arlington, VA, June 2015.

- D.J. DeVoto. 2015. "Performance and Reliability of Bonded Interfaces for High-Temperature Packaging." Presentation to the DOE Vehicle Technologies Office (VTO) Electrical and Electronics Technical Team, Southfield, MI, May 2015.

- D.J. DeVoto. 2014. "Performance and Reliability of Bonded Interfaces for High-Temperature Packaging." Electric Drive Technologies Program FY15 Kickoff Meeting, DOE Vehicle Technologies Office, Oak Ridge, TN, November 2014.

- 6. D.J. DeVoto, A.A. Wereszczak, and P.P. Paret. 2014. "Stress Intensity of Delamination in a Sintered-Silver Interconnection." IMAPS High Temperature Electronics (HiTEC), Albuquerque, NM.

#### Acknowledgments

The author would like to acknowledge the support provided by Susan Rogers and Steven Boyd, Technology Development Managers for the EDT Program, Vehicle Technologies Office, U.S. Department of Energy Office of Energy Efficiency and Renewable Energy. The significant contributions of Andrew Wereszczak, Paul Paret, and Jake Callaghan are acknowledged.

#### References

- A.A. Wereszczak, Z. Liang, M.K. Ferber, L.D. Marlino, 2014. "Uniqueness and Challenges of Sintered Silver as a Bonded Interface Material," International Conference on High Temperature Electronics (HiTEC), Albuquerque, NM, 2014.

- 2. R.W. Chuang, C.C. Lee, 2002. "Silver-Indium Joints Produced at Low Temperature for High Temperature Devices," IEEE Transactions on Components and Packaging Technologies, Vol. 25, No. 3, pp. 453–458.

- 3. K. Sow, 2014. "Are Sintered Silver Joints Ready for Use as Interconnect Material in Microelectronic Packaging?" Journal of Electronic Materials, Vol. 43, No. 4; pp. 947–961.

- 4. S.W. Yoon, K. Shiozaki, S. Yasuda, and M.D. Glover, 2012. "Highly reliable nickel-tin transient liquid phase bonding technology for high temperature operational power electronics in electrified vehicles" Twenty-Seventh Annual IEEE Applied Power Electronics Conference and Exposition (APEC), 478–482.

- 5. H. Greve and F.P. McCluskey, 2014. "LT-TLPS Die Attach for High Temperature Electronic Packaging," Journal of Microelectronics and Electronic Packaging, Vol. 11, No. 1, pp. 7–15.

- 6. D.J. DeVoto, A.A. Wereszczak, and P.P. Paret. 2014. "Stress Intensity of Delamination in a Sintered-Silver Interconnection." IMAPS High Temperature Electronics (HiTEC), Albuquerque, NM.

- 7. R. Darveaux and K. Banerji. 1992. "Constitutive Relations for Tin-Based Solder Joints," IEEE Transactions on Components, Hybrids, and Manufacturing Technology, Vol. 15, No. 6; pp. 1013–1024.

- 8. G. Bai. 2005. "Low-Temperature Sintering of Nanoscale Silver Paste for Semiconductor Device Interconnection," PhD Thesis.