# Inverter Ground Fault Overvoltage Testing

Andy Hoke, Austin Nelson, and Sudipta Chakraborty *National Renewable Energy Laboratory*

Justin Chebahtah, Trudie Wang, and Michael McCarty SolarCity Corporation

NREL is a national laboratory of the U.S. Department of Energy Office of Energy Efficiency & Renewable Energy Operated by the Alliance for Sustainable Energy, LLC

This report is available at no cost from the National Renewable Energy Laboratory (NREL) at www.nrel.gov/publications.

Technical Report NREL/TP-5D00-64173 August 2015

Contract No. DE-AC36-08GO28308

# Inverter Ground Fault Overvoltage Testing

Andy Hoke, Austin Nelson, and Sudipta Chakraborty National Renewable Energy Laboratory

Justin Chebahtah, Trudie Wang, and Michael McCarty SolarCity Corporation

Prepared under Task No. ST13.IN11

NREL is a national laboratory of the U.S. Department of Energy Office of Energy Efficiency & Renewable Energy Operated by the Alliance for Sustainable Energy, LLC

This report is available at no cost from the National Renewable Energy Laboratory (NREL) at www.nrel.gov/publications.

National Renewable Energy Laboratory 15013 Denver West Parkway Golden, CO 80401 303-275-3000 • www.nrel.gov **Technical Report** NREL/TP-5D00-64173 August 2015

Contract No. DE-AC36-08GO28308

#### NOTICE

This report was prepared as an account of work sponsored by an agency of the United States government. Neither the United States government nor any agency thereof, nor any of their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States government or any agency thereof.

This report is available at no cost from the National Renewable Energy Laboratory (NREL) at www.nrel.gov/publications.

Available electronically at SciTech Connect http://www.osti.gov/scitech

Available for a processing fee to U.S. Department of Energy and its contractors, in paper, from:

U.S. Department of Energy Office of Scientific and Technical Information P.O. Box 62 Oak Ridge, TN 37831-0062 OSTI <u>http://www.osti.gov</u> Phone: 865.576.8401 Fax: 865.576.5728 Email: <u>reports@osti.gov</u>

Available for sale to the public, in paper, from:

U.S. Department of Commerce National Technical Information Service 5301 Shawnee Road Alexandria, VA 22312 NTIS <u>http://www.ntis.gov</u> Phone: 800.553.6847 or 703.605.6000 Fax: 703.605.6900 Email: <u>orders@ntis.gov</u>

Cover Photos by Dennis Schroeder: (left to right) NREL 26173, NREL 18302, NREL 19758, NREL 29642, NREL 19795.

## **Acknowledgments**

The National Renewable Energy Laboratory (NREL) thanks SolarCity and the U.S. Department of Energy (DOE) Solar Energy Technologies Office for cost-share funding of this work.

Additionally, the authors would like to thank Frances Bell, Krutak Kamdar, Brian Zimmerly, and Ryan Hanley from SolarCity; Colton Ching, Anthony Hong, Demy Bucaneg, Marc Asano, Reid Ueda, Shaun Imada, Kandice Kubojiri, Steven Rymsha, Melanie Higa, and Riley Ceria from the Hawaiian Electric Companies; Ben York and Aminul Huque from the Electric Power Research Institute; Phil Barker of Nova Energy Specialists; and Mariko Shirazi and Adam Bailey of NREL for their valuable input and support. We also thank the members of the Forum on Inverter Grid Integration Issues (FIGII, formerly known as the Industry Task Force on Effective Grounding, ITFEG), led by Brian Lydic of Fronius USA, for providing the test plan that served as the basis for the test procedure used in this study. Finally, we are greatly indebted to Michael Ropp of Northern Plains Power Technologies for his background work, valuable technical input, and detailed review of report drafts.

### **Executive Summary**

Various interconnection challenges exist when connecting distributed PV into the electrical distribution grid in terms of safety, reliability, and stability of electric power systems. One of the urgent areas for additional research - as identified by inverter manufacturers, installers, and utilities – is the potential for transient overvoltage from PV inverters. In one stage of a cooperative research and development agreement, NREL is working with SolarCity to address two specific types of transient overvoltage: load rejection overvoltage (LRO) and ground fault overvoltage (GFO). Additional partners in this effort include the Hawaiian Electric Companies, Northern Plains Power Technologies, and the Electric Power Research Institute.

This report describes testing conducted at NREL to determine the duration and magnitude of transient overvoltages created by several commercial PV inverters during ground fault conditions. For this work, a test plan developed by the Forum on Inverter Grid Integration Issues (FIGII) has been implemented in a custom test setup at NREL. Load rejection overvoltage test results were reported previously in a separate technical report.

The GFO tests were completed on three commercial inverters: a single-stage, three-phase string inverter; a dual-stage, three-phase string inverter, and a three-phase assembly of single-phase microinverters. All inverters tested had transformerless topologies. The dual-stage, three-phase string inverter was also tested with two different transformers connected at its output: a wye-grounded:wye-grounded transformer and a delta:wye-grounded transformer. Each inverter was tested at unity power factor and at minimum leading and lagging power factors. Results confirm previous theoretical analyses asserting that inverters do not drive ground-fault overvoltages in the same way that synchronous machines do, although they can do so to a limited extent in certain scenarios<sup>1</sup>. The total voltage duration and the maximum continuous time above various line-neutral voltage thresholds are presented here, as well as other test parameters. We also present brief investigations into the effects of changing inverter overvoltage and overfrequency trip settings, the effect of anti-islanding controls, and the effect of delta- and wye-connected loads. Finally, we quantify line-line overvoltage magnitudes and durations as well, showing that three-phase inverters can cause low levels of line-neutral overvoltage due to power rejection from the faulted phase to the unfaulted phases.

It is very important to note that the GFO test method used here is designed to scientifically investigate inverter-driven GFO, and <u>is not designed</u> to exactly emulate ground-fault conditions on a real distribution feeder. Therefore the test procedure and test results are not intended for certification testing. Also note that these tests do not attempt to investigate the wide range of possible load conditions and circuit configurations that may be present on a feeder during a ground fault. Instead, the intent is to create conditions that isolate the inverter ground fault response from other effects.

<sup>&</sup>lt;sup>1</sup> Inverters *can* drive overvoltages via other mechanisms, such as power rejection to unfaulted phases (explained below in this report) and load rejection overvoltage (see http://www.nrel.gov/docs/fy15osti/63510.pdf).

## Contents

|   | Acknowledgments                                                 |      |

|---|-----------------------------------------------------------------|------|

|   | Executive Summary                                               | ii   |

|   | Contents                                                        |      |

|   | Tables                                                          | . vi |

| 1 | Introduction                                                    | 1    |

| 2 | Test Procedures                                                 | 3    |

|   | 2.1 GFO Test Procedure                                          | 4    |

|   | 2.2 GFO Data Reporting                                          | 7    |

|   | 2.3 Test Inverters and Test Equipment Description               | 8    |

| 3 | Test Results                                                    | .11  |

|   | 3.1 RLC Load Tuning                                             | .11  |

|   | 3.2 Total Time Above Voltage Thresholds                         | . 13 |

|   | 3.3 Maximum Continuous Time Above Voltage Thresholds            | .17  |

|   | 3.4 Maximum Instantaneous Overvoltage                           | . 19 |

|   | 3.5 Trip Time / Time to Disconnect                              | . 22 |

|   | 3.6 Waveforms of Interest                                       | 24   |

|   | 3.7 Effect of Voltage and Frequency Trip Settings               | 39   |

|   | 3.8 Comparison of GFO Test Versions: AI Enabled vs. AI Disabled |      |

|   | 3.9 Tests with Transformers                                     |      |

|   | 3.10 Tests with Delta-connected Load                            | 59   |

|   | 3.11 Line to Line Voltage Analysis                              | . 66 |

| 4 | Conclusions and Future Work                                     |      |

|   | References                                                      | .76  |

|   |                                                                 |      |

## Figures

| Figure 1: Generalized schematic of GFO test setup                                                                  | 4   |

|--------------------------------------------------------------------------------------------------------------------|-----|

| Figure 2: Generalized schematic of GFO test setup with transformer                                                 | 5   |

| Figure 3: Example waveform depicting how test result data is defined                                               | 8   |

| Figure 4: Example plot of overvoltage duration as a function of voltage threshold level and power factor for a sin | gle |

| test inverter                                                                                                      | 14  |

| Figure 5: Cumulative overvoltage durations for Inverter 1                                                          | 15  |

| Figure 6: Cumulative overvoltage durations for Inverter 2                                                          |     |

| Figure 7: Cumulative overvoltage durations for Inverter 3. Note vertical range extends to only 0.25 ms.            |     |

| Figure 8: Maximum continuous overvoltage durations for Inverter 1                                                  |     |

| Figure 9: Maximum continuous overvoltage duration times for Inverter 2                                             |     |

| Figure 10: Maximum continuous overvoltage duration times for Inverter 3                                            |     |

| Figure 11: Maximum instantaneous overvoltage vs. power factor for Inverter 1                                       |     |

| Figure 12: Maximum instantaneous overvoltage vs. power factor for Inverter 2                                       |     |

| Figure 13: Maximum instantaneous overvoltage vs. power factor for Inverter 3                                       |     |

| Figure 14: Trip time as a function of power factor for Inverter 1                                                  |     |

| Figure 15: Trip time as a function of power factor for Inverter 2                                                  |     |

| Figure 16: Trip time as a function of power factor for Inverter 3                                                  |     |

| Figure 17: Inverter 1 waveform at unity power factor (test SC0005)                                                 |     |

| Figure 18: Symmetrical components of Inverter 1 voltage waveforms at unity power factor (test SC0005)              |     |

| Figure 19: A close-up of the waveforms in Figure 17 at the time of the fault                                       |     |

| Figure 19: A close-up of the wavelorms in Figure 17 at the time of the fault.                                      |     |

| Figure 21: Symmetrical components of the voltage for Inverter 1 test with longest cumulative overvoltage           | 20  |

| (SAO0003)                                                                                                          | 20  |

|                                                                                                                    |     |

| Figure 22: One of the mildest overvoltages produced by Inverter 1 (SBU0005)                                        |     |

| Figure 23: Typical line to line voltages of Inverter 1 (SCO0005)                                                   |     |

| Figure 24: Inverter 2 baseline islanding test (EI_0007).                                                           |     |

| Figure 25: Close-up of island transient in Inverter 2 baseline islanding test (EI_0007)                            |     |

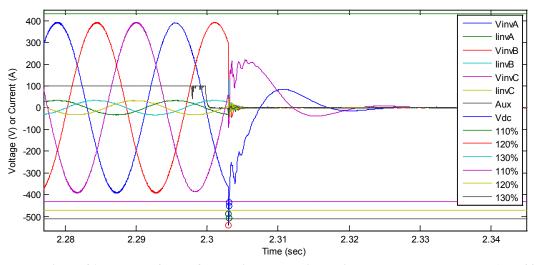

| Figure 26: Inverter 2 waveforms showing fast output shutdown (EB_0003)                                             |     |

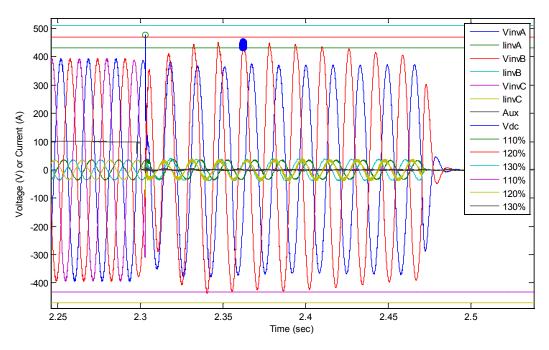

| Figure 27: Inverter 2 waveforms showing longer run-on (EC+_0003)                                                   |     |

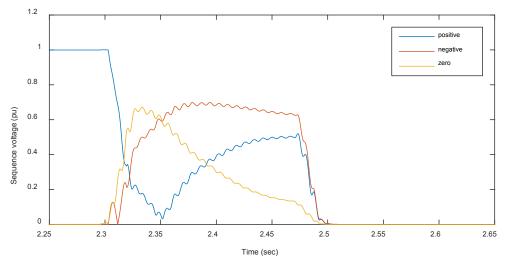

| Figure 28: Symmetrical voltage components for Inverter 2 test with longer run-on (EC+_0003)                        |     |

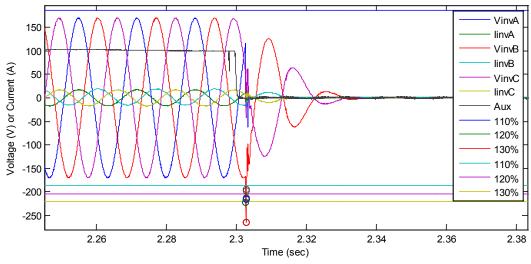

| Figure 29: Inverter 2 waveforms showing the longest overvoltage at the 110% level (EC+_0001)                       |     |

| Figure 30: Symmetrical components of Inverter 2 voltages for the test with longest overvoltage at the 110% level   |     |

| (EC+_0001)                                                                                                         |     |

| Figure 31: Inverter 2 waveforms with the maximum instantaneous overvoltage (EB_0005)                               |     |

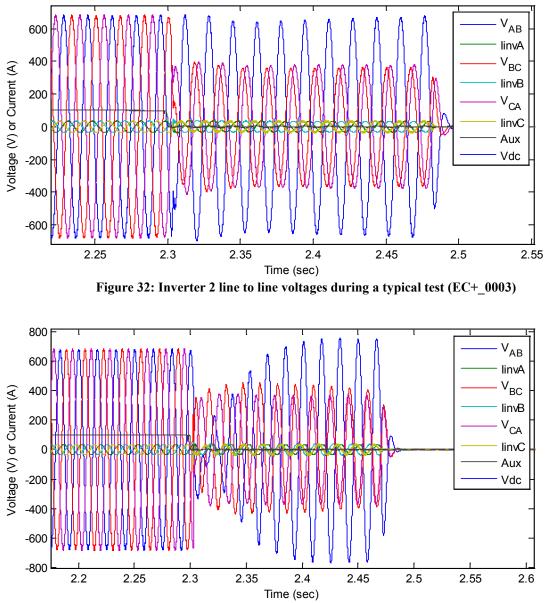

| Figure 32: Inverter 2 line to line voltages during a typical test (EC+_0003)                                       |     |

| Figure 33: Inverter 2 line to line waveforms for the test with the longest cumulative overvoltage (EC+_0001)       |     |

| Figure 34: Inverter 3 baseline islanding test (NILD0000)                                                           |     |

| Figure 35: Close-up of island transient in Inverter 3 baseline islanding test (NILD0000)                           |     |

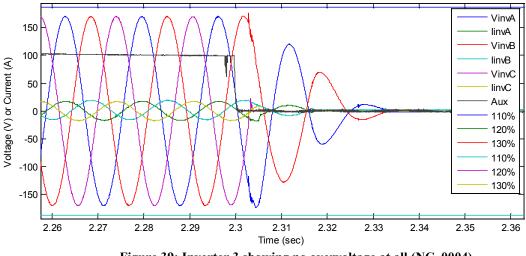

| Figure 36: Typical Inverter 3 waveform (NC_0003)                                                                   |     |

| Figure 37: A variation of the typical Inverter 3 waveform (NB_0002)                                                |     |

| Figure 38: Inverter 3 worst-case peak overvoltage (NA_0006)                                                        |     |

| Figure 39: Inverter 3 showing no overvoltage at all (NC_0004)                                                      |     |

| Figure 40: Inverter 3 line to line voltages during a typical test (NC_0003)                                        |     |

| Figure 41: Examining the dependence of GFO response on voltage and frequency trip settings for Inverter 1          |     |

| Figure 42: Examining the dependence of peak overvoltage on trip settings for Inverter 1                            |     |

| Figure 43: Examining the dependence of ground-fault disconnection time on trip settings for Inverter 1             |     |

| Figure 44: Baseline anti-islanding test for Inverter 1 (SA1A0001)                                                  |     |

| Figure 45: Anti-islanding test with AI controls disabled for Inverter 1 (ILND0000)                                 | 43  |

| Figure 46: Comparison of GFO test results for Inverter 1 using test Version 1 (Islanded) and Version 2             |     |

| (Immediate).                                                                                                       | 44  |

| Figure 47: Comparison of GFO test maximum overvoltage and trip time for Inverter 1 using test Version 1            |     |

| (Islanded) and Version 2 (Immediate).                                                                              |     |

| Figure 48: GFO test of Inverter 1 using test Version 2 (AI enabled) (SA1A0003).                                    |     |

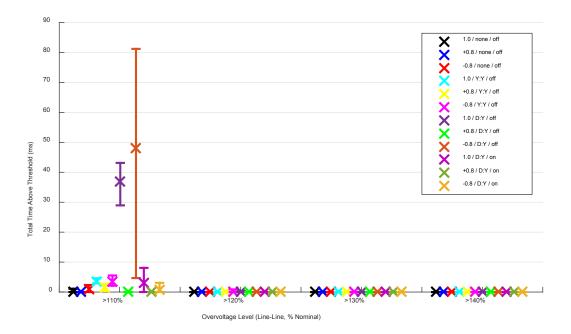

| Figure 49: Cumulative overvoltage durations for tests with and without transformers                                | 47  |

This report is available at no cost from the National Renewable Energy Laboratory (NREL) at www.nrel.gov/publications.

| Figure 50: Continuous overvoltage durations for tests with and without transformers                              | 48 |

|------------------------------------------------------------------------------------------------------------------|----|

| Figure 51: Peak overvoltages for tests with and without transformers                                             |    |

| Figure 52: Trip times for tests with and without transformers                                                    |    |

| Figure 53: Typical unity power factor test with Y:Y transformer (SA Y0002)                                       |    |

| Figure 54: Symmetrical components of a typical unity power factor test with Y:Y transformer (SA Y0002)           | 51 |

| Figure 55: Typical lagging power factor test with D:Y transformer (SAOD0000)                                     |    |

| Figure 55: Symmetrical voltage components for a typical lagging power factor test with D:Y transformer           |    |

| (SAOD0000)                                                                                                       | 53 |

| Figure 56: Typical leading power factor test with D:Y transformer (SBUD0001)                                     | 54 |

| Figure 57: Typical leading power factor test with D:Y transformer, zoomed in (SBUD0001)                          | 55 |

| Figure 58: Comparison of overvoltage durations with AI disabled and enabled, with D:Y transformer                | 56 |

| Figure 59: Comparison of peak overvoltages and trip times with AI disabled and enabled, with D:Y transformer     | 56 |

| Figure 60: Typical unity power factor test with D:Y transformer and AI enabled (AY1D0011)                        | 57 |

| Figure 61: A less common response type for unity power factor tests with D:Y transformer and AI enabled          |    |

| (AY1D0008)                                                                                                       |    |

| Figure 62: A typical lagging power factor test with D:Y transformer and AI enabled (ADOD0006)                    |    |

| Figure 63: A typical test with D:Y transformer and delta load, with AI disabled (S_DD0001)                       |    |

| Figure 64: A typical test with D:Y transformer and delta load, with AI disabled (S_DD0001)                       |    |

| Figure 63: Symmetrical components during a typical test with D:Y transformer and delta load, with AI disabled    |    |

| (S_DD0001)                                                                                                       |    |

| Figure 65: A typical test with no transformer and delta load, with AI disabled (S1U_0003)                        |    |

| Figure 66: Line to line overvoltages for Inverter 1, with and without voltage and frequency ride-through         |    |

| Figure 67: Line-line voltages in a typical test with no transformer (SCO0005)                                    |    |

| Figure 68: Line-line voltages showing slightly increasing voltage and current magnitudes (SCO0003)               |    |

| Figure 69: Line to line overvoltages for Inverter 2                                                              | 70 |

| Figure 70: Line-line voltages for a typical test of Inverter 2 (EC_0005). Note that currents and voltages remain | _  |

| near-nominal, in contrast to those of Inverter 1. Also note that DC current falls and acquires a strong 120 H    |    |

| component after the fault because one of the phases (phase C) is no longer exporting power                       |    |

| Figure 71: Peak line-line voltages for Inverter 3                                                                |    |

| Figure 72: Cumulative line to line overvoltage times for tests with transformers. Tests with delta-wye transform |    |

| are shown both with AI disabled and AI enabled, to emphasize that worst-case overvoltages are mitigated b        |    |

| having AI on.                                                                                                    |    |

| Figure 73: Peak line to line overvoltages for tests with transformers                                            | 72 |

| Figure 74: Current and line to line voltage waveforms for a test with delta-wye transformer and AI disabled      |    |

| (SD1D0004). Note the increase in current magnitudes at the inverter output due to power rejection to the         |    |

| unfaulted phases.                                                                                                | 73 |

## Tables

| Table 1: GFO Test Versions                                                                                     |    |

|----------------------------------------------------------------------------------------------------------------|----|

| Table 2. Overvoltage threshold levels                                                                          | 7  |

| Table 3: Basic test inverter specifications                                                                    | 9  |

| Table 4: Transformer configurations for additional tests                                                       | 9  |

| Table 5: Inverter 1 Load Settings – Unity Power Factor                                                         | 12 |

| Table 6: Inverter 1 Load Settings – Leading Power Factor                                                       | 12 |

| Table 7: Inverter 1 Load Settings – Lagging Power Factor                                                       | 12 |

| Table 8: Inverter 2 Load Settings – Unity Power Factor                                                         | 12 |

| Table 9: Inverter 2 Load Settings – Leading Power Factor                                                       | 13 |

| Table 10: Inverter 2 Load Settings – Lagging Power Factor                                                      | 13 |

| Table 11: Inverter 3 Load Settings – Unity Power Factor                                                        |    |

| Table 12: Maximum total time above each voltage threshold (ms)                                                 | 14 |

| Table 13: Average total time above each voltage threshold (ms)                                                 | 15 |

| Table 14: Maximum continuous time above each voltage threshold (ms)                                            | 17 |

| Table 15: Average of maximum continuous times above each voltage threshold (ms)                                | 17 |

| Table 16: Maxima of maximum instantaneous voltage measurements (% of nominal peak)                             |    |

| Table 17: Average of maximum instantaneous voltage measurements (% of nominal peak)                            |    |

| Table 18: Maximum time to disconnect for all inverters (ms)                                                    |    |

| Table 19: Average time to disconnect for all inverters (ms)                                                    |    |

| Table 20: Inverter 1 default voltage and frequency trip settings (IEEE 1547-2003)                              | 40 |

| Table 21: Inverter 1 widened voltage and frequency trip settings                                               |    |

| Table 22: Maximum total time (ms) above each voltage threshold – transformers                                  |    |

| Table 23: Average total time (ms) above each voltage threshold – transformers                                  |    |

| Table 24: Maximum continuous time (ms) above each voltage threshold with and without transformers              |    |

| Table 25: Average continuous time (ms) above each voltage threshold with and without transformers              |    |

| Table 26: Maximum total time (ms) above each voltage threshold with D:Y transformer - AI off and AI on         | 55 |

| Table 27: Average maximum total time (ms) above each voltage threshold with D:Y transformer – AI off and       |    |

| AI on                                                                                                          |    |

| Table 28: Maximum total time (ms) above each voltage threshold with delta load, with AI disabled               |    |

| Table 29: Average total time (ms) above each voltage threshold with delta load, with AI disabled               |    |

| Table 30: Maximum continuous time (ms) above each voltage threshold with delta load, with AI disabled          |    |

| Table 31: Average maximum continuous time (ms) above each voltage threshold with delta load, with AI disable   |    |

| Table 32: Maximum total time (ms) above each voltage threshold with D:Y transformer and delta load - AI off    |    |

| AI on                                                                                                          |    |

| Table 33: Average total time (ms) above each voltage threshold with D:Y transformer and delta load - AI off ar | ıd |

| AI on                                                                                                          | 66 |

## **1** Introduction

The proliferation of inverter-coupled technologies such as solar photovoltaics (PV) on electric distribution systems has resulted in new opportunities to optimize distribution power systems and has created new challenges to prevent unstable or damaging conditions. This project addresses an urgent utility concern: the potential for transient or temporary overvoltage (TOV) from inverter-based generation such as solar PV. Transient or temporary overvoltage is of concern because of the potential to cause damage to nearby equipment and loads [1], [2]. There are two types of TOV that are of primary concern for inverter-coupled generation: load rejection overvoltage (LRO) and ground fault overvoltage (GFO) [3].

This report focuses on experimental testing of GFO. LRO testing was covered separately in previous publications [4], [5]. GFO can occur on a three-phase distribution system following a single line to ground fault: voltage-source generation may enforce line-to-line voltage relationships resulting in an overvoltage with respect to neutral on the un-faulted phases.

Some previous work has been interpreted (or misinterpreted) to recommended uniform GFO mitigation measures for all distributed energy resources, both machine-based and inverter-based [1]. However, other authors have indicated that while GFO is a concern with synchronous machine generation and can be mitigated through effective grounding<sup>2</sup>, the same is not necessarily true for inverter-based generation [3]. GFO can be a concern for inverter sources in some cases, but it is generally more easily mitigated and is less of a problem than GFO of synchronous rotating machines. Inverters, which are best modeled as current sources from the grid's perspective, do not enforce the line-to-line voltage relationship at their output terminals and hence should not cause GFO in the same way as synchronous machines. Moreover, in the scenarios where inverters could contribute to GFO, effective grounding - as defined in IEEE 142 [7] – is not expected to solve the problem [3]. This result has been confirmed through simulation but has not been previously verified experimentally. The testing described herein is intended to fill that gap by experimentally evaluating in what scenarios PV inverters cause GFO, and to what extent. As such, the test plan used is designed to isolate the response of the PV inverter to a ground fault, and not to exactly simulate the wide range of ground fault conditions possible on real distribution feeders. The test result analysis focuses primarily on line to neutral voltages, which are of concern in classic GFO response, but also delves briefly into line to line voltage responses. Symmetrical components are plotted for selected tests to provide insight into the effect that removal of zero sequence components through effective grounding would have on ground fault responses.

<sup>&</sup>lt;sup>2</sup> Definitions of effective grounding vary. See the IEEE C62.92 series, for example [6]. According to some definitions, a system is considered effectively grounded if a ground fault does not produce overvoltages above a certain level; in some cases inverters may inherently fulfil this definition. In practice, effective grounding requirements may be fulfilled by installing grounding transformers, a practice that is sometimes very useful and sometimes not. Detailed definitions of effective grounding and recommendations for effective grounding solutions are beyond the scope of this report.

This report describes GFO testing of a selection of common PV inverters in accordance with a newly-developed test plan. An industry group known as the Forum on Inverter Grid Integration Issues (FIGII), which consists of members from inverter manufacturers, utilities, consultants, and research labs, developed the test plan through a consensus-based process. A total of three inverters were tested, and one of the inverters was also tested with wye-grounded:wye-grounded (Y:Y) and delta:wye-grounded (D:Y) transformers connected between the test inverter and the ground fault location. While the largest inverter tested here is rated at 20 kW, the physical effects tested are not functions of inverter size, so conclusions drawn from testing are representative of all current-controlled inverters (a category that includes the vast majority of grid-tied PV inverters). The testing described here serves to provide feedback to stakeholders and is being used to provide input to inverter model development. An upcoming publication will further analyze the theory behind inverter ground fault responses and expand on the results presented here [8].

It is worth briefly reviewing what happens in a typical field scenario following a single line-toground fault. Distribution circuits and faults vary widely, but some elements are common to most single line to ground faults. When a single line to ground fault occurs, the fault often causes an upstream breaker or recloser to open, isolating the faulted part of the circuit from the rest of the grid. If there is distributed generation in the isolated (islanded) section, the generation will briefly power any load within the island until the generator's controller recognizes the island and ceases power exportation. This can result in TOV via two mechanisms, mentioned above. The mechanism of primary concern to this report is GFO, in which a three-wire generator can cause a zero-sequence voltage to appear when feeding a four-wire circuit during a single phase to ground fault. The second TOV mechanism, LRO, occurs if the generation to load ratio within the island is greater than unity. Both of these mechanisms can occur together following a single line to ground fault if an island forms with more generation than load. LRO can also occur on its own when an island forms in the absence of a single line to ground fault, as quantified in [4], [5]. This report describes experiments designed to characterize inverter GFO response in isolation from LRO and other transient effects, to the extent possible.

## 2 Test Procedures

The test procedure used to evaluate the behavior of inverters in ground fault scenarios is based on a GFO test plan written by the FIGII working group. This test plan was designed to allow the inverter's ground fault response to be observed for as long as possible, and in isolation from the islanding event. The specific test procedures used at NREL, which include one test version that adheres very closely to the FIGII procedure and another modified test version, are described below. Both test versions use a resonant load to allow the inverter-load circuit to be as stable as possible when the ground fault is created with the grid simulator disconnected. Briefly, the GFO test consists of four steps:

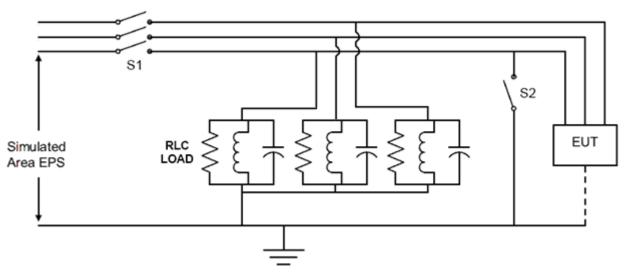

- 1. Connect the test inverter to the test setup as shown in Figure 1.

- Tune the resistive-inductive-capacitive (RLC) load so that the current from the grid simulator (also known as the Simulated Area EPS (electric power system) [9]) is nearly zero and so that the load resonates at 60 Hz with a qualify factor (QF) of roughly unity.

- 3. Remove the grid simulator from the circuit, creating an island. Steps 1 through 3 are very similar to the IEEE 1547.1 test for unintentional islanding [10].

- 4. Create the ground fault and record voltage waveforms.

These four steps are broken down into a detailed test procedure in the next subsection.

Ideally the test is performed with the inverter's anti-islanding (AI) controls disabled. This allows a stable inverter-load island to form following step 3 before the ground fault is created, which in turn allows the ground fault behavior to persist (within the constraints of inverter protection settings) and to be observed in the absence of other dynamics.

One test inverter was not able to disable AI, and another uses a type of controller that cannot readily form a stable island (i.e. the AI method is integral to the controls). When testing these two inverters, the fault was formed immediately after the grid simulator was removed (within half of a 60 Hz line cycle) using an automatic relay circuit.

Hence there are two versions of the GFO test, as shown in Table 1. Version 1, with AI disabled, is the preferred version, as written by FIGII.

| GFO Test  | Priority | AI control | Time between island | Comments                                                                    |

|-----------|----------|------------|---------------------|-----------------------------------------------------------------------------|

| Version   |          | status     | creation and fault  |                                                                             |

| Version 1 | Primary  | Disabled   | $\geq 2$ seconds    | • Requires ability to form stable island.                                   |

|           |          |            |                     | <ul> <li>No separate baseline test needed.</li> </ul>                       |

| Version 2 | Backup   | Active     | 3-5 milliseconds    | • May be difficult to separate island transient from ground-fault behavior. |

|           |          |            |                     | <ul> <li>Requires AI testing as baseline.</li> </ul>                        |

Table 1: GFO Test Versions

Recall that the intent of these tests is not to replicate the range of load and circuit conditions that are found in the field, but rather to observe the inverter's ground fault behavior with minimal interference from other phenomena. Cases where the generation to load ratio varies from unity are not tested here because it would not be possible to form a stable island, and thus it would be difficult to clearly see the effect in the tests. In cases where the generation to load ratio is greater than one when a ground fault occurs, the inverter behavior would be a combination of its ground fault response and the LRO response, as characterized in [4], [5]. As in [4] and [5], the duration of this combined response would likely be short, especially in cases of higher generation to load ratio.

The detailed test procedure is described below. Much of the language is taken directly from the FIGII test procedure document, which in turn borrowed some language from IEEE Std 1547.1.

## 2.1 GFO Test Procedure

For these tests, any active voltage regulation features available in the equipment under test (EUT, i.e. the inverter) were disabled. Also, if any of the inverters tested as part of this work had required an external or separate transformer, the transformer would have been connected between the EUT and the load specified in Figure 1 and would have been considered part of the product being tested. None of the inverters tested required external transformers, although where indicated some tests were performed with transformers connected between the EUT and the rest of the circuit to determine the impact of the transformer configuration on GFO.

Figure 1: Generalized schematic of GFO test setup

The test circuit was configured as shown in Figure 1. The neutral connection (grounded conductor) was unaffected by the operation of switch S1. The balanced load circuit shown in the figure was applied from each phase to neutral (wye configuration) unless otherwise indicated. Switch S1 was gang-operated and multi-pole. Switch S2 was applied between one phase and ground. Inverters 1 and 3 are believed to have no low-impedance power connection to neutral. Inverter 2, however, is believed to have a power connection to neutral.

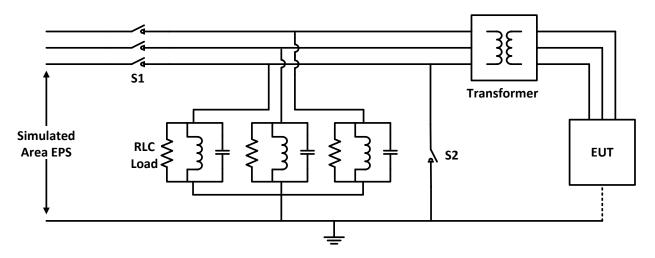

The test setup for tests with transformers is shown in Figure 2; it differs from Figure 1 only in the insertion of a three-phase transformer between the EUT and S2. All line to neutral voltages on both sides of the transformer were measured. For delta-wye transformer tests, the delta side faced the fault location (S2). All transformer neutral connections were grounded.

Figure 2: Generalized schematic of GFO test setup with transformer

Each EUT was connected according to the instructions and specifications provided by the manufacturer. All EUT input source parameters were set to the nominal operating conditions for the EUT. All EUT settings were set to default values unless otherwise indicated, with two exceptions: 1) AI controls were disabled if running test Version 1, and 2) the 300-second countdown timer to begin power export was disabled in order to shorten the time between tests.

The test sequence for test Version 1 was as follows, with modifications for Version 2 shown in blue:

- a) Connect the EUT according to the instructions and specifications provided by the manufacturer.

- b) Set all EUT input source parameters to the nominal operating conditions for the EUT.

- c) Set (or verify) all EUT parameters to the nominal operating settings. *Island detection functions were disabled for this test, if possible.* (If running Version 2, leave island detection functions enabled.)

- d) Set the EUT (including the input source as necessary) to provide 100% of its rated output power.

- e) Record all applicable settings.

- f) Set the simulated EPS to the EUT nominal voltage  $\pm 2\%$  and nominal frequency  $\pm 0.1$  Hz.

- g) Adjust the islanding load circuit in Figure 1 to provide a quality factor  $Q_f$  of at least 1.0 (when  $Q_f$  is equal to 1.0, the following applies:  $P_{qL} = P_{qC} = 1.0 \times P$ ). The value of  $Q_f$  is to be determined by using the following equations as appropriate:

$$Q_f = R \sqrt{\frac{C}{L}}$$

or

$$Q_f = \frac{\sqrt{P_{\rm qL} \times P_{\rm qC}}}{P}$$

where

$Q_{\rm f}$  is the quality factor of the parallel RLC resonant load,

*R* is the effective load resistance ( $\Omega$ ),

*C* is effective load capacitance (F),

*L* is effective load inductance (H),

$P_{qL}$  is the reactive power per phase consumed by the inductive load component (VARS),  $P_{qC}$  is the reactive power per phase consumed by the capacitive load component (VARS), P is the real output power per phase of the unit (W),

The inductance and capacitance are to be calculated using the following equations:

$$L = \frac{V^2}{2 \times \pi \times f \times P \times Q_f}$$

$$C = \frac{P \times Q_f}{2 \times \pi \times f \times V^2}$$

where

V is the nominal voltage across each phase of the RLC load (V) (for loads connected phase to phase, V is the nominal line-line voltage; for loads connected phase to neutral, V is the nominal phase-neutral voltage),

f is frequency (Hz).

When tuning for the current balance in this step with a non-unity output power factor EUT, there will be an imbalance between the *L* and *C* load components to account for the EUT reactive current. The EUT reactive output current shall be measured and algebraically added to the appropriate reactive load component when calculating  $Q_{\rm f}$ .

- h) Close switch S1 and wait until the EUT produces the desired power level.

- i) Adjust *R*, *L*, and *C* until the fundamental frequency current through switch S1 is less than 2% of the rated current of the EUT on a steady-state basis in each phase.

- j) Open switch S1 and allow a stable island to form with voltage within 10% of nominal and frequency within 0.5% of nominal. If running Version 2 (anti-islanding enabled), do not wait for a stable island to form.

- k) Begin recording the voltage measurement.

- Close switch S2 and record the voltage until the EUT ceases to energize the RLC load or until voltage has stabilized. If running Version 2, close switch S2 immediately after opening switch S1 to maximize the island duration.

- m) Repeat the test four times for a total of five tests.

- n) Repeat steps e) through m) with switch S2 connected to the other phases until all phases have been tested.

- o) Repeat steps e) through n) at the minimum power factors for the EUT, both capacitive and inductive.

#### Requirements

The EUT input sources used were capable of supplying at least 150% of the maximum input power rating of the EUT over the entire range of EUT input voltages. The test and measurement equipment recorded each phase current and each phase-to-neutral and phase-to-phase voltage over the duration of the test. A sampling frequency of at least 10 kHz was required. Sampling frequencies of 50 kHz were used in most tests unless otherwise indicated.

The equations for  $Q_f$  are based upon an ideal parallel RLC circuit. For this reason, non-inductive resistors, low loss (high Q) inductors, and capacitors with low effective series resistance and effective series inductance were utilized in the test circuit. Power ratings of resistors were conservatively chosen to minimize thermally induced drift in resistance values during the course of the test.

## 2.2 GFO Data Reporting

A voltage-duration curve was created using sampled instantaneous voltage measurements during the complete transient time of the inverter. The number of voltage measurements above the voltage levels provided in Table 2 was multiplied by the sample interval, resulting in that voltage threshold's total duration. The voltage-duration curve is a plot of all points (voltage, duration) derived from this process. Because classic GFO affects line-neutral voltages, all results reported herein are for line-neutral voltages unless otherwise indicated.

| Instantaneous Voltage |  |  |  |

|-----------------------|--|--|--|

| (% of nominal peak)   |  |  |  |

| 170                   |  |  |  |

| 140                   |  |  |  |

| 130                   |  |  |  |

| 120                   |  |  |  |

| 110                   |  |  |  |

#### Table 2. Overvoltage threshold levels

The voltage levels shown in Table 2 are significantly modified from voltage levels in what is known as the CBEMA<sup>3</sup> curve, or its successor the ITIC<sup>4</sup> curve, both of which describe the tolerance of electronic equipment to voltage surges of varying durations. The voltage levels have been modified to better characterize inverter behavior across the range of voltage levels expected during testing. FIGII working group members generally agreed that the CBEMA and

<sup>&</sup>lt;sup>3</sup> Computer Business Equipment Manufacturers Association

<sup>&</sup>lt;sup>4</sup> Information Technology Industry Council

ITIC curves may not actually be appropriate for evaluating inverter behavior in transient overvoltage scenarios because they were not designed for that purpose. However, more appropriate curves are not known to have been developed, and their development would require significant research and consensus building. Also note that the voltage levels used here differ from those used in the LRO testing presented in [4] in that they are more concentrated at lower overvoltage levels to provide better granularity to the analysis at the expected TOV levels.

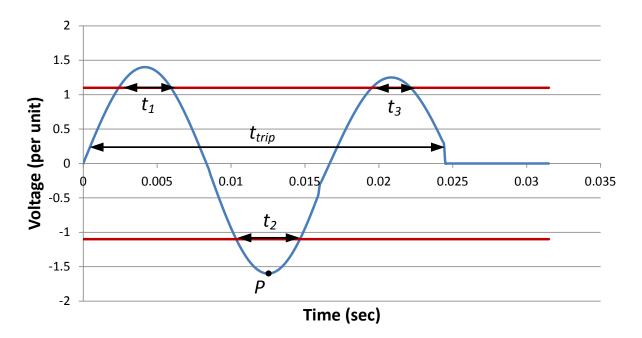

In addition, the longest time that the voltage exceeded each of the limits in Table 2 *continuously* was recorded for each of the test settings. The distinction between the total voltage duration and the maximum continuous duration is depicted in Figure 3. For waveforms that exceed a defined voltage threshold during multiple parts of the cycle (either positive or negative polarity), the total voltage duration will always be greater than the maximum continuous time. For the example waveform given, the total voltage duration would be recorded as the sum of  $t_1$ ,  $t_2$ , and  $t_3$ . Since  $t_2$  is the longest continuous time the voltage exceeds the threshold,  $t_2$  would be recorded for the longest continuous duration metric.

Figure 3: Example waveform depicting how test result data is defined

In addition to the voltage duration metrics described, the absolute value of the maximum instantaneous voltage measurement recorded at any time during the transient event is reported (as represented by the voltage at point P in Figure 3), as well as the trip time (represented by  $t_{trip}$ ). For the purposes of these tests, the trip time was defined as the time between switch S2 closing and the EUT current dropping below a threshold and never again exceeding that threshold.

### 2.3 Test Inverters and Test Equipment Description

The basic specifications for the test inverters are given in Table 3. For the purposes of this report, the inverter manufacturer and model number are not given, and inverters are given a generic

name ("Inverter 1", Inverter 2", ...). As seen in Table 3, a variety of inverter topologies and power levels have been selected for this study.

When describing leading and lagging power factor throughout this report, the generator reference frame is used: current is defined as positive when leaving the inverter. Hence lagging power factor operation corresponds to sourcing of reactive power (sometimes called overexcited operation in analogy to rotating machine controls), and leading power factor operation corresponds to sinking of reactive power (analogous to underexcited machine operation). To avoid confusion, this explanation is reiterated in each section of this report.

For Inverter 1, the minimum power factor was 0.8, both leading and lagging. Inverter 2 can operate at nearly any power factor, but the minimum power factor listed in the data sheet was 0.8 (both leading and lagging), so 0.8 was used as the minimum power factor for GFO testing purposes. Inverter 3 can only operate at unity power factor.

|               | Voltage<br>Configuration | Nameplate<br>Power | Additional<br>Information                                         | Test<br>Version | Minimum<br>Leading PF | Minimum<br>Lagging PF |

|---------------|--------------------------|--------------------|-------------------------------------------------------------------|-----------------|-----------------------|-----------------------|

| Inverter<br>1 | 480 V Three<br>Phase     | 12.0 kW            | Dual stage,<br>transformerless                                    | 1               | 0.8                   | 0.8                   |

| Inverter 2    | 480 V Three<br>Phase     | 20.0 kW            | Single stage,<br>transformerless                                  | 2               | 0.8                   | 0.8                   |

| Inverter<br>3 | 208 V Three<br>Phase     | 4.5 kW             | (18) 250 W<br>microinverters in a<br>three-phase<br>configuration | 2               | NA                    | NA                    |

Table 3: Basic test inverter specifications

Table 4 shows the configurations of the two transformers used for additional tests of Inverter 1. Only Inverter 1 was tested with transformers.

| Table 4: Transformer configurations | for additional tests |

|-------------------------------------|----------------------|

|-------------------------------------|----------------------|

| Transformer Configuration |                                              | Transformer Rated Power | <b>Turns Ratio</b> |  |

|---------------------------|----------------------------------------------|-------------------------|--------------------|--|

| Inverter 1                | Wye-grounded:Wye-grounded                    | 30 kVA                  | 1:1                |  |

| Inverter 1                | Delta:Wye-grounded<br>(Wye on inverter side) | 30 kVA                  | 1:1                |  |

The major test and measurement equipment used in this testing were as follows:

- Grid Simulator: Ametek MX45 45 kVA AC power supply (bi-directional)

- DC Input Source (central/string inverters): MagnaPower MTD1000-250 DC power supply

- DC Input Source (microinverters): TerraSAS PV supply, 14x ETS60X14C-PVF and 4x ETS80X10.5C-PVF modules

- Load Banks: LoadTec 250 kVA RLC load bank, wye-connected. Minimum load step sizes at 480 VAC are 50 W and 50 VARs, both capacitive and inductive.

- Yokogawa DL750E Scopecorder, calibration date 08/2014, 701260 modules for power measurements, 701250 modules for signal measurements. AC voltages directly input to sensing modules.

- Yokogawa DL850E Scopecorder, calibration date 08/2014, 720210/701250 modules for power measurements, 701267 modules for signal measurements. AC voltages directly input to sensing modules.

- Hioki 9693 AC/DC current probes with 6590 transducers

- Yokogawa 701930 current probes (10 mV/A, 150/500 A maximum)

- Fluke 87 RMS multimeter

## **3 Test Results**

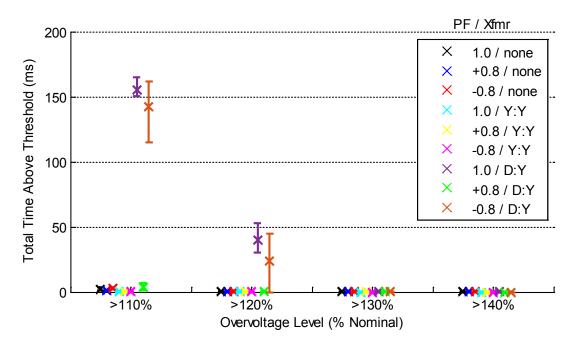

All test results for GFO testing are provided in the following sections for each of the three test inverters. Each section contains mean values and maximum/minimum values for each of the inverter/load power test settings, across a typical total of 21 tests (seven for each phase) at each setting. While the test procedure called for five tests per phase, in many cases seven tests were run. The first sections contain data about total overvoltage durations, maximum continuous overvoltage durations, maximum voltage measurements, and trip times, focusing on line to neutral voltages. Representative waveforms and waveforms of particular interest are provided in the subsequent section for each test inverter. Representative island transition waveforms are also presented, as these serve as a baseline under test Version 2. Finally, the following comparative analyses are presented:

- Default voltage and frequency trip settings versus wide trip settings

- Test Version 1 (AI disabled) versus test Version 2 (AI enabled)

- No transformer versus Y:Y transformer versus D:Y transformer

- Wye-connected load versus delta-connected load

- Analysis of line to line voltages

## 3.1 RLC Load Tuning

The power and reactive power settings of the RLC load for each test category are given in Table 5 through Table 11. Note that these settings refer to the power of the load bank itself rather than the entire circuit, which contains some additional resistance, inductance, and capacitance. For this reason when the circuit is tuned so that inverter real power matches circuit power dissipation, the load bank real power is always somewhat less than the inverter output power. For non-unity power factor tests, the real power values are further reduced because the inverters curtailed active power in order to produce reactive power. Inverter 3 was not capable of operating at non-unity power factor.

Also note that the exact tuning of the load is not as crucial in GFO tests as it is in unintentional islanding tests: in GFO tests the purpose of the island is primarily to allow the inverter to run without being connected to an AC voltage source. This is true of both Version 1 (AI disabled) and Version 2 (AI enabled) of the GFO test. Nevertheless, load quality factors of nearly 1.0 or slightly higher were used.

Each phase of the load bank employed was individually tunable, and in many tests each phase was individually tuned to minimize fundamental frequency current from the grid simulator (i.e. to optimize the matching between load and generation). When per-phase load values are not given, the load was balanced. Unless otherwise stated, the tests described below used the load bank settings given in the following tables, where P is the real power setting,  $Q_L$  is the inductive reactive power setting, and  $Q_C$  is the capacitive reactive power setting:

| <i>P</i> (kW) | 11.4 |  |

|---------------|------|--|

| $Q_L$ (kVAR)  | 12.3 |  |

| $Q_C$ (kVAR)  | 12.0 |  |

Table 5: Inverter 1 Load Settings – Unity Power Factor

#### Table 6: Inverter 1 Load Settings – Leading<sup>5</sup> Power Factor

| <i>P</i> (kW) | 9.3  |  |

|---------------|------|--|

| $Q_L$ (kVAR)  | 8.5  |  |

| $Q_C$ (kVAR)  | 15.5 |  |

Table 7: Inverter 1 Load Settings – Lagging Power Factor

|                    | Phase A | Phase B | Phase C |

|--------------------|---------|---------|---------|

| <b>P</b> (kW) 2.95 |         | 5.25    | 2.83    |

| $Q_L$ (kVAR)       | 5.25    | 5.25    | 5.25    |

| $Q_C$ (kVAR)       | 2.85    | 2.75    | 2.70    |

Table 8: Inverter 2 Load Settings – Unity Power Factor

|               | Phase A | Phase B | Phase C |

|---------------|---------|---------|---------|

| <i>P</i> (kW) | 6.25    | 6.15    | 6.05    |

| $Q_L$ (kVAR)  | 6.65    | 6.65    | 6.65    |

| $Q_C$ (kVAR)  | 6.85    | 6.65    | 6.85    |

<sup>&</sup>lt;sup>5</sup> The generator reference frame is used in this report: lagging power factor corresponds to sourcing reactive power, and leading power factor corresponds to sinking reactive power.

|               | Phase A | Phase B | Phase C |

|---------------|---------|---------|---------|

| <i>P</i> (kW) | 4.80    | 4.70    | 4.70    |

| $Q_L$ (kVAR)  | 3.50    | 3.50    | 3.0     |

| $Q_C$ (kVAR)  | 7.35    | 7.35    | 7.35    |

Table 9: Inverter 2 Load Settings – Leading<sup>5</sup> Power Factor

#### Table 10: Inverter 2 Load Settings – Lagging<sup>5</sup> Power Factor

|               | Phase A | Phase B | Phase C |  |

|---------------|---------|---------|---------|--|

| <i>P</i> (kW) | 5.00    | 5.00    | 4.80    |  |

| $Q_L$ (kVAR)  | 7.85    | 7.85    | 7.75    |  |

| $Q_C$ (kVAR)  | 3.50    | 3.50    | 3.50    |  |

Table 11: Inverter 3 Load Settings – Unity Power Factor

|               | Phase A | Phase B | Phase C |

|---------------|---------|---------|---------|

| <i>P</i> (kW) | 1.35    | 1.35    | 1.35    |

| $Q_L$ (kVAR)  | 1.55    | 1.65    | 1.55    |

| $Q_C$ (kVAR)  | 1.50    | 1.55    | 1.50    |

## 3.2 Total Time Above Voltage Thresholds

The total overvoltage duration curves for each of the three test inverters are provided below. These plots display the total amount of time that the voltage at the AC terminals exceeded each of the voltage thresholds given in Table 2. Each measurement is inclusive of higher threshold limits; for example, time above the 120% threshold includes time above the 130%, 140%, and 170% thresholds. Each measurement represents the total time that any of the three phases exceeded a given threshold (the sum of the three phases).

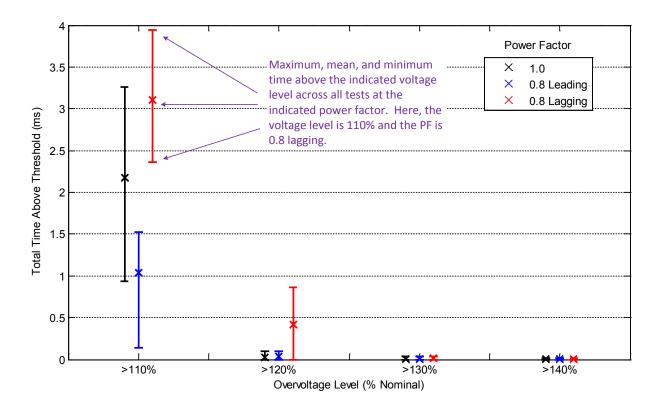

An example overvoltage duration plot is shown in Figure 4. The legend shows each of the three inverter power factor settings, and a plot is given at each of these test settings for each voltage threshold. Each whisker plot shows the average (mean) value of the test runs, along with the maximum and minimum values of these tests.

Figure 4: Example plot of overvoltage duration as a function of voltage threshold level and power factor<sup>6</sup> for a single test inverter

The overall test data are summarized in Table 12 and Table 13, which contain all of the information about averages and maxima that is contained in individual inverter plots. All time measurements are reported in milliseconds (ms). Inverter 3 was not capable of operating at non-unity power factor. For the standard wye-load tests without transformers, no overvoltage levels reached the 170% threshold, and all overvoltage times were quite brief. Most of the overvoltages above 120% were due to a very brief initial current spike through the fault rather than to longer time-scale effects, as will be clear from the voltage waveforms presented further below.

|             |      | Inver       | ter 1 |      |      | Inver | ter 2 |      |      | Inver | ter 3 |      |

|-------------|------|-------------|-------|------|------|-------|-------|------|------|-------|-------|------|

| Inverter PF | 110% | <b>120%</b> | 130%  | 140% | 110% | 120%  | 130%  | 140% | 110% | 120%  | 130%  | 140% |

| 1.0         | 3.26 | 0.10        | 0.04  | 0.02 | 0.14 | 0.08  | 0.04  | 0.00 | 0.22 | 0.10  | 0.04  | 0.02 |

| 0.8 leading | 1.52 | 0.10        | 0.04  | 0.02 | 0.18 | 0.08  | 0.02  | 0.00 | -    | -     | -     | -    |

| 0.8 lagging | 3.94 | 0.86        | 0.04  | 0.02 | 6.36 | 0.06  | 0.02  | 0.00 | -    | -     | -     | -    |

Table 12: Maximum total time above each voltage threshold (ms)

<sup>&</sup>lt;sup>6</sup> The generator reference frame is used in this report: lagging power factor corresponds to sourcing reactive power, and leading power factor corresponds to sinking reactive power.

|             |      | Inver         | ter 1 |      |      | Inve          | rter 2 |      |      | Inver | ter 3 |      |

|-------------|------|---------------|-------|------|------|---------------|--------|------|------|-------|-------|------|

| Inverter PF | 110% | 1 <b>20</b> % | 130%  | 140% | 110% | 1 <b>20</b> % | 130%   | 140% | 110% | 120%  | 130%  | 140% |

| 1.0         | 2.18 | 0.03          | 0.01  | 0.00 | 0.06 | 0.02          | 0.00   | 0.00 | 0.08 | 0.03  | 0.01  | 0.01 |

| 0.8 leading | 1.04 | 0.04          | 0.01  | 0.00 | 0.07 | 0.02          | 0.00   | 0.00 | -    | -     | -     | -    |

| 0.8 lagging | 3.10 | 0.42          | 0.01  | 0.00 | 0.51 | 0.01          | 0.00   | 0.00 | -    | -     | -     | -    |

Table 13: Average total time above each voltage threshold (ms)

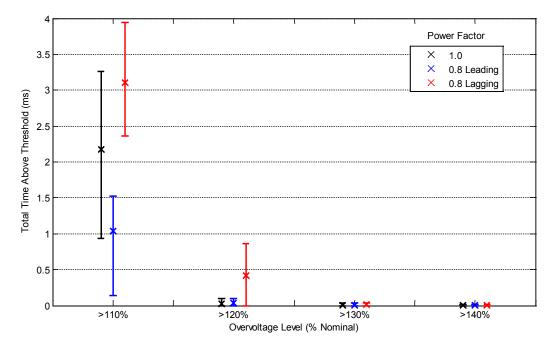

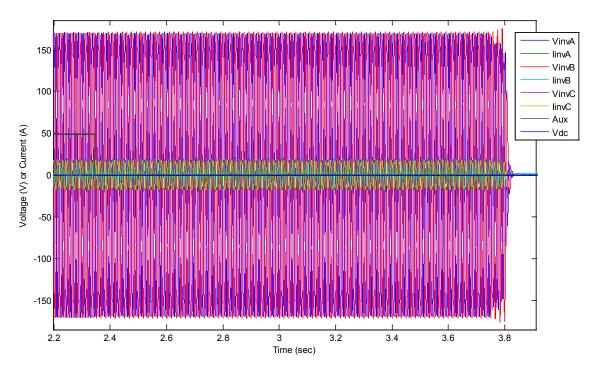

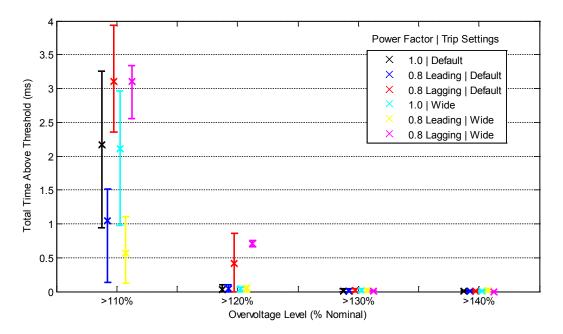

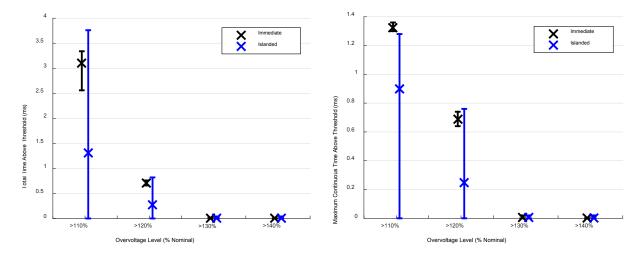

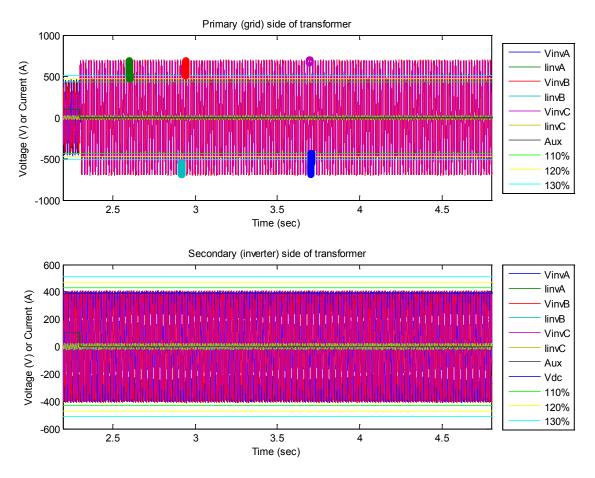

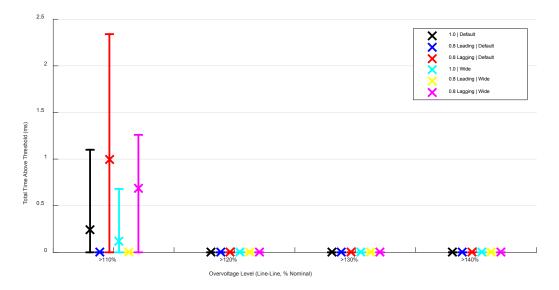

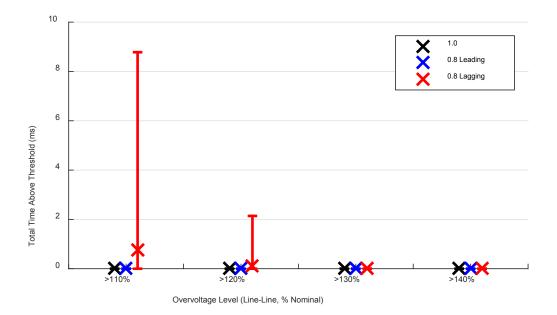

A plot of the voltage duration ranges for Inverter 1 is shown in Figure 5. The largest measured overvoltage duration above 110% of nominal was under 4 ms and the largest duration above 120% of nominal was under 1 ms. Overvoltage durations tended to be longest for lagging power factor and shortest for leading power factor, and this inverter had few overvoltage measurements above the 140% threshold.

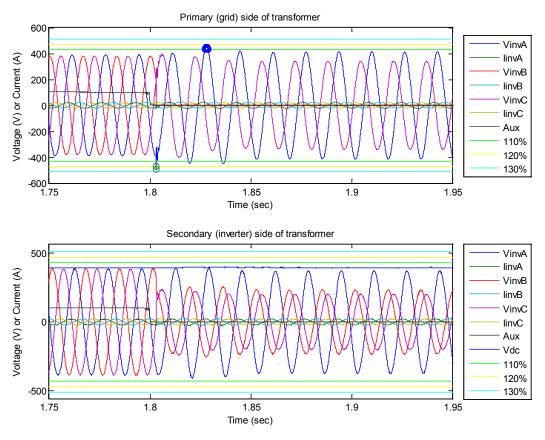

Figure 5: Cumulative overvoltage durations for Inverter 1

A plot of the overvoltage duration ranges for Inverter 2 is shown in Figure 6. Nearly all overvoltage cumulative durations were below 1 ms. The largest measured overvoltage duration above 110% of nominal was 6.4 ms. This inverter spent very little time above the 120% threshold. Like Inverter 1, Inverter 2 also shows worst-case overvoltages with lagging power factor.

Figure 6: Cumulative overvoltage durations for Inverter 2

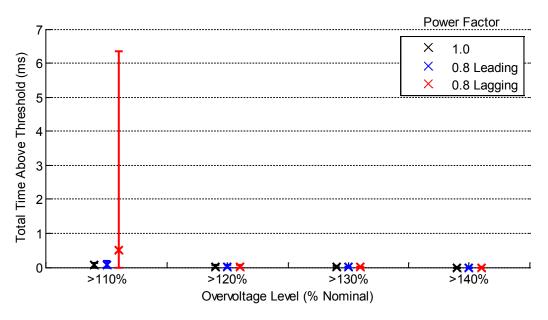

A plot of the voltage duration ranges for Inverter 3 is shown in Figure 7. This inverter is not capable of operating at non-unity power factor, so only unity power factor results are shown. The largest measured overvoltage duration above 110% of nominal was under 0.25 ms. This inverter showed the shortest overvoltage durations of the three inverters.

Figure 7: Cumulative overvoltage durations for Inverter 3. Note vertical range extends to only 0.25 ms.

All three inverters produced very short cumulative overvoltages, totaling below half of an AC line cycle in all cases shown above. Tests with transformers and with delta-connected loads have not been included above and are described later.

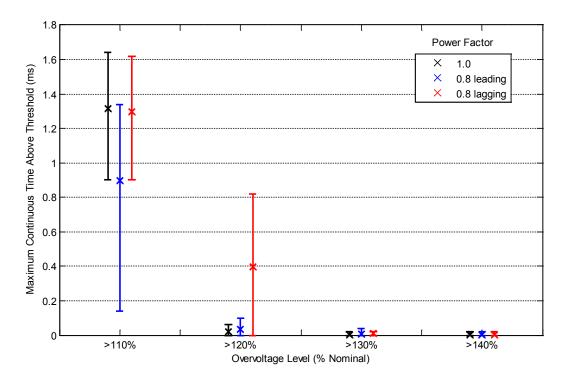

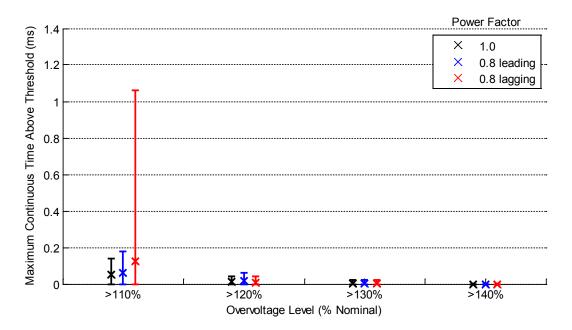

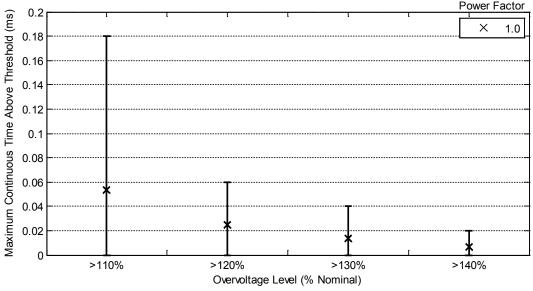

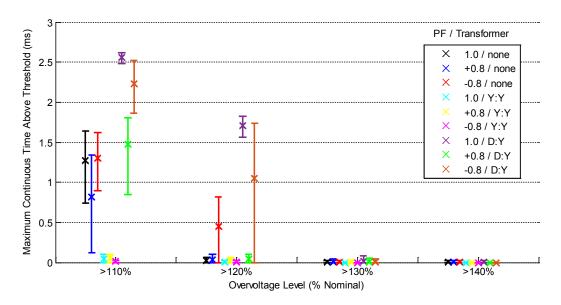

## 3.3 Maximum Continuous Time Above Voltage Thresholds

Summaries of the maximum and average of the maximum continuous time spent above each voltage threshold are shown in Table 14 and Table 15. Since no instantaneous voltage measurement exceeded 170% of nominal, only the 110%/120%/130%/140% thresholds are reported in these tables. As described earlier, the maximum continuous time variables by definition are less than or equal to the total time durations reported in the previous section. Averages and maxima are calculated from a set of tests (typically 21, seven for each phase) executed at each loading ratio. This data set shows the maximum continuous time that any individual phase voltage exceeded a given threshold. It is possible that the maximum continuous overvoltage occurred on different phases for different voltage thresholds. No inverter exceeded 2 ms continuously above any threshold for any of these transformerless, wye-load tests.

|                          |      | Inver         | ter 1 |      |      | Inver | ter 2 |      |      | Inver | ter 3 |      |

|--------------------------|------|---------------|-------|------|------|-------|-------|------|------|-------|-------|------|

| Inverter $\mathbf{PF}^7$ | 110% | 1 <b>20</b> % | 130%  | 140% | 110% | 120%  | 130%  | 140% | 110% | 120%  | 130%  | 140% |

| 1.0                      | 1.64 | 0.06          | 0.02  | 0.02 | 0.14 | 0.04  | 0.02  | 0.00 | 0.18 | 0.06  | 0.04  | 0.02 |

| 0.8 leading              | 1.34 | 0.10          | 0.04  | 0.02 | 0.18 | 0.06  | 0.02  | 0.00 | -    | -     | -     | -    |

| 0.8 lagging              | 1.62 | 0.82          | 0.02  | 0.02 | 1.06 | 0.04  | 0.02  | 0.00 | -    | -     | -     | -    |

Table 14: Maximum continuous time above each voltage threshold (ms)

|             |      | Inver | ter 1 |      |      | Inve | rter 2 |      |      | Inver | ter 3 |      |

|-------------|------|-------|-------|------|------|------|--------|------|------|-------|-------|------|

| Inverter PF | 110% | 120%  | 130%  | 140% | 110% | 120% | 130%   | 140% | 110% | 120%  | 130%  | 140% |

| 1.0         | 1.32 | 0.02  | 0.00  | 0.00 | 0.05 | 0.01 | 0.00   | 0.00 | 0.05 | 0.02  | 0.01  | 0.01 |

| 0.8 leading | 0.90 | 0.03  | 0.01  | 0.00 | 0.06 | 0.02 | 0.00   | 0.00 | -    | -     | -     | -    |

| 0.8 lagging | 1.30 | 0.40  | 0.01  | 0.00 | 0.13 | 0.01 | 0.00   | 0.00 | -    | -     | -     | -    |

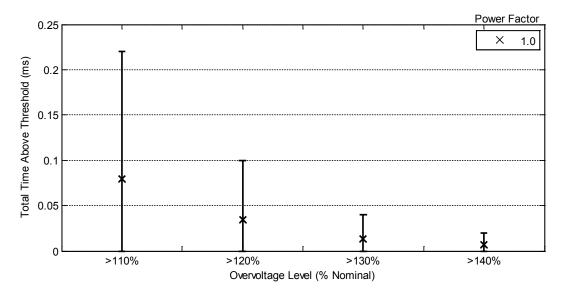

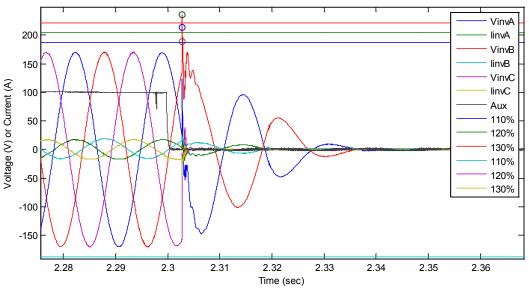

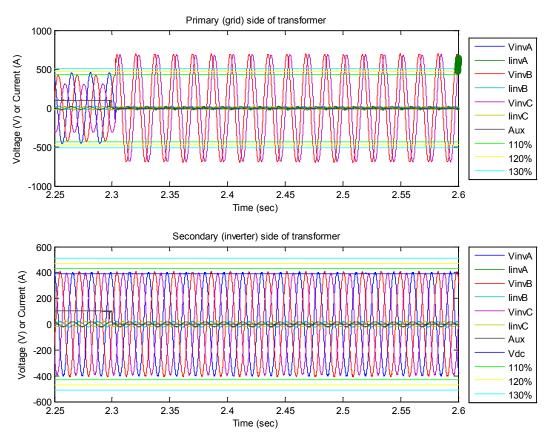

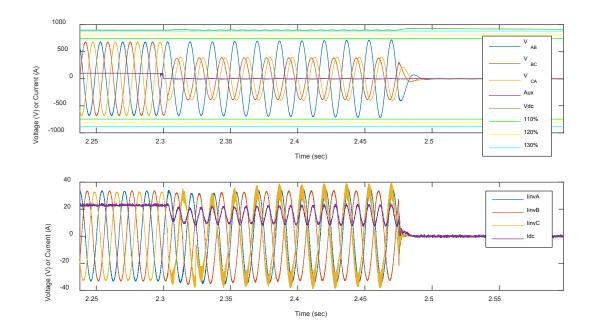

A plot of the maximum continuous overvoltage duration ranges for Inverter 1 is shown in Figure 8. The largest measured continuous overvoltage duration above 110% of nominal was under 1.7 ms. Again, worst-case overvoltage durations occurred for lagging power factor operation.

<sup>&</sup>lt;sup>7</sup> The generator reference frame is used in this report: lagging power factor corresponds to sourcing reactive power, and leading power factor corresponds to sinking reactive power.

Figure 8: Maximum continuous overvoltage durations for Inverter 1

A plot of the maximum continuous overvoltage duration ranges for Inverter 2 is shown in Figure 9. The largest measured continuous overvoltage duration above 110% of nominal was under 1.2 ms. Again, worst-case overvoltage duration came at lagging power factor.

Figure 9: Maximum continuous overvoltage duration times for Inverter 2

This report is available at no cost from the National Renewable Energy Laboratory (NREL) at www.nrel.gov/publications.

A plot of the maximum continuous overvoltage duration ranges for Inverter 3 is shown in Figure 10. The largest measured continuous overvoltage duration above 110% of nominal was under 2 ms. This inverter had consistently short continuous overvoltage times.

Figure 10: Maximum continuous overvoltage duration times for Inverter 3

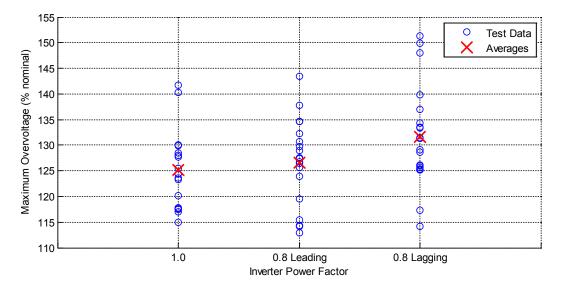

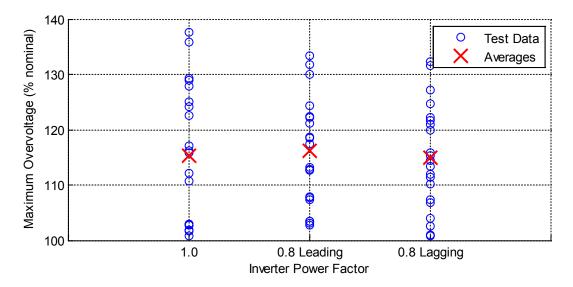

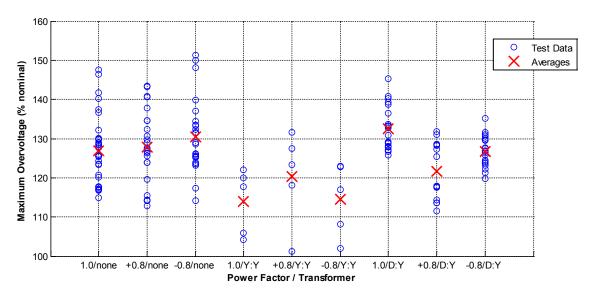

## 3.4 Maximum Instantaneous Overvoltage

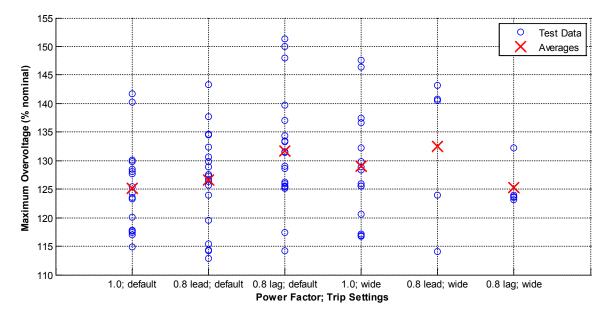

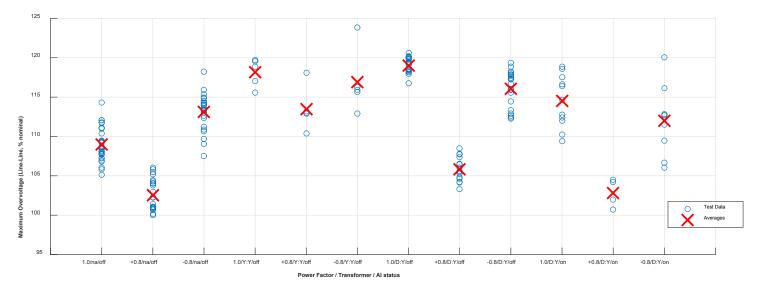

This section presents data on the maximum instantaneous overvoltage measurement recorded at any point during the fault transient event. Averages and maximums across (typically) 21 different tests at each power factor are provided in Table 16 and Table 17. The plots in this section and the next display the parameter of interest as a function of inverter power factor. Each plot shows the average across all tests at a given power factor (red "X") as well as the individual test data points (blue circles). As discussed below with the voltage waveforms, the peak overvoltage is typically due to the very brief fault transient (rather than to a quasi-steady-state sinusoidal overvoltage typically associated with GFO) and is highly dependent on where in the sinusoid the fault occurs.

Table 16: Maxima of maximum instantaneous voltage measurements (% of nominal peak)

| Inverter PF <sup>8</sup> | Inverter 1 | Inverter 2 | Inverter 3 |

|--------------------------|------------|------------|------------|

| 1.0                      | 142        | 138        | 156        |

| 0.8 leading              | 143        | 133        | -          |

| 0.8 lagging              | 151        | 132        | -          |

<sup>&</sup>lt;sup>8</sup> The generator reference frame is used in this report: lagging power factor corresponds to sourcing reactive power, and leading power factor corresponds to sinking reactive power.

| Inverter PF | Inverter 1 | Inverter 2 | Inverter 3 |

|-------------|------------|------------|------------|

| 1.0         | 125        | 115        | 129        |

| 0.8 leading | 127        | 116        | -          |

| 0.8 lagging | 132        | 115        | -          |

Table 17: Average of maximum instantaneous voltage measurements (% of nominal peak)

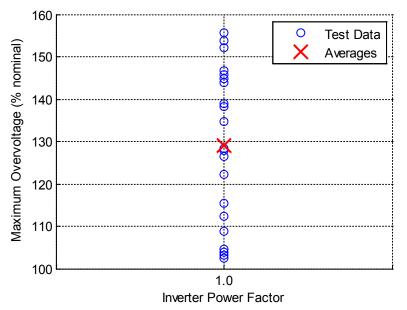

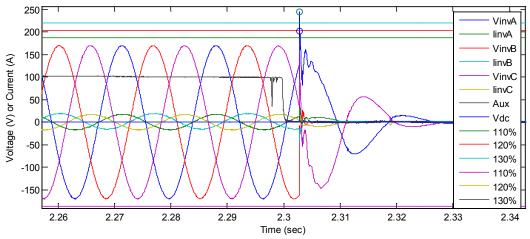

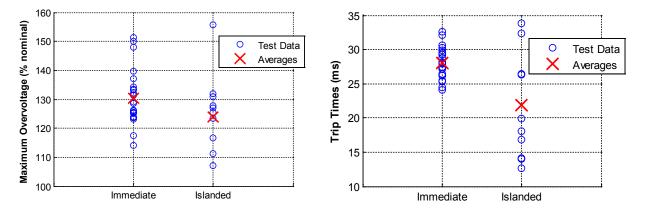

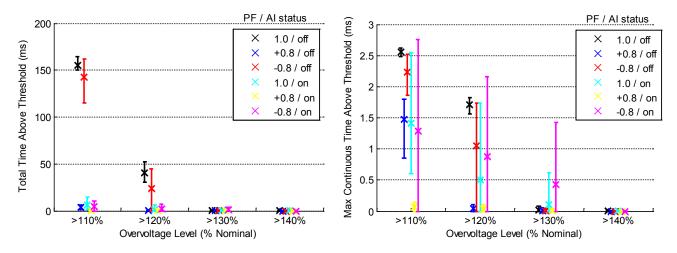

The maximum instantaneous overvoltages measured as a function of power factor for Inverter 1 are found in Figure 11. Peak overvoltages fell in a wide range starting as low as 113% above nominal, and going as high as 151% of nominal. (Note: this could also be phrased as 51% *above* nominal.) As with overvoltage durations, maximum voltage levels tend to be somewhat worse at lagging power factor.

Figure 11: Maximum instantaneous overvoltage vs. power factor for Inverter 1

The maximum instantaneous overvoltages measured as a function of power factor for Inverter 2 are found in Figure 12. Peak voltages cover a wide range starting well within ANSI Range A and going as high as 138% of nominal. Inverter 2 tended to have slightly lower instantaneous overvoltage levels compared to the other two inverters. For this inverter, lagging power factor tests did not show higher overvoltage levels, though they did show somewhat longer overvoltage durations.

Figure 12: Maximum instantaneous overvoltage vs. power factor for Inverter 2

The maximum instantaneous overvoltages measured for Inverter 3 are found in Figure 13. The maximum voltage measured during any of the tests of Inverter 3 was 156% of nominal, and the lowest maximum voltage was very near to the nominal voltage. Recall, as mentioned previously and shown in Figure 10, that the higher overvoltages had very short durations; the highest peak overvoltages lasted only one sample cycle (0.02 ms).

Figure 13: Maximum instantaneous overvoltage vs. power factor for Inverter 3

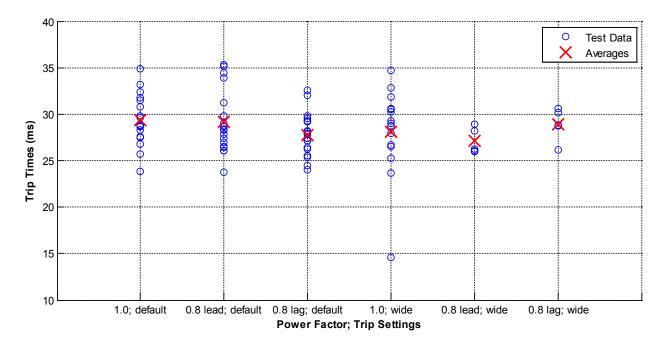

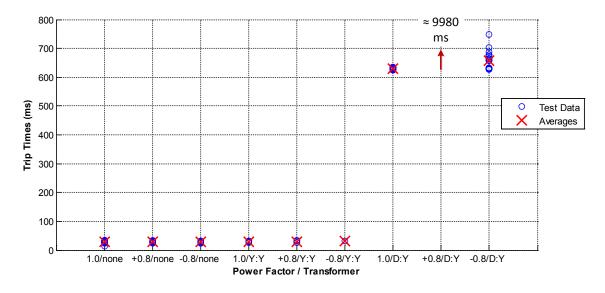

## 3.5 Trip Time / Time to Disconnect

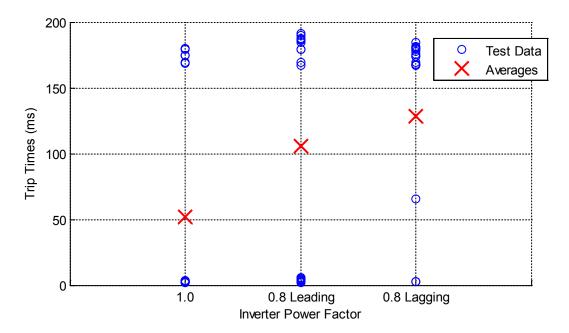

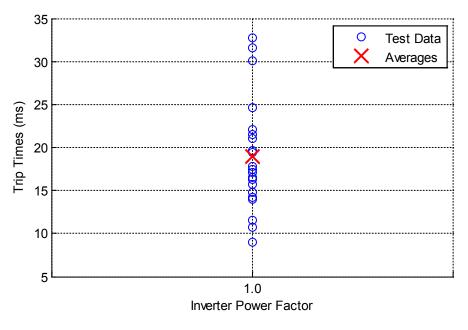

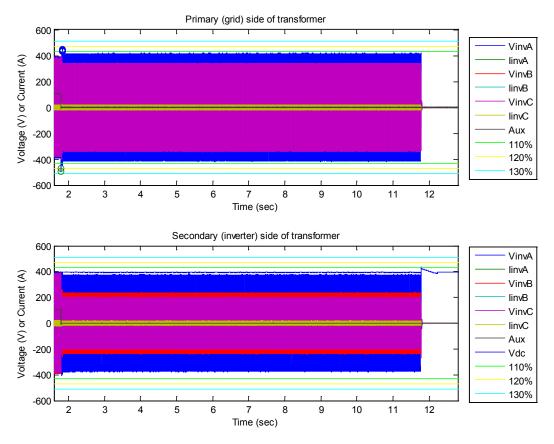

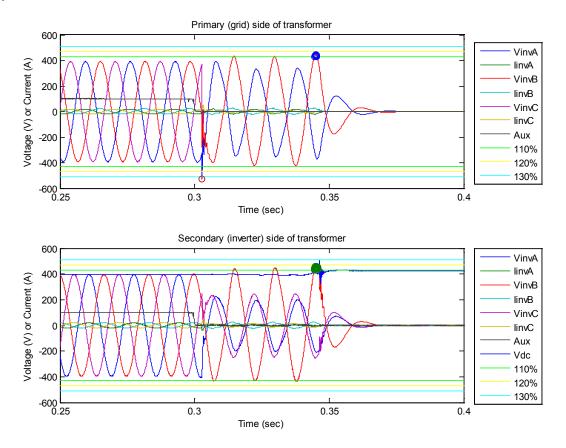

This section shows data about the trip time (also called time to disconnect or run-on time) for each test inverter as a function of power factor. For the purposes of this testing, the trip time was defined as the time from switch S2 closing (see Figure 1) until the time that each phase current ceased to exceed a threshold of 3 A peak. This threshold was chosen empirically as the optimal level to detect inverter turn-off given signal noise and offset. Maxima and averages across typically 21 different tests at each power factor are provided in Table 18 and Table 19. Inverters 1 and 3 tended to disconnect after two AC line cycles. Inverter 2 displayed a binary behavior, sometimes disconnecting in under one cycle but sometimes running for roughly ten cycles at near-nominal line-neutral voltage magnitude.

| Inverter PF <sup>9</sup> | Inverter 1 | Inverter 2 | Inverter 3 |

|--------------------------|------------|------------|------------|

| 1.0                      | 34.9       | 180.0      | 32.7       |

| 0.8 leading              | 35.3       | 191.5      | -          |

| 0.8 lagging              | 32.6       | 184.3      | -          |

Table 18: Maximum time to disconnect for all inverters (ms)

|             | -          |            |            |

|-------------|------------|------------|------------|

| Inverter PF | Inverter 1 | Inverter 2 | Inverter 3 |

| 1.0         | 29.4       | 51.7       | 18.9       |

| 0.8 leading | 29.2       | 105.5      | -          |

| 0.8 lagging | 27.8       | 128.5      | -          |

Table 19: Average time to disconnect for all inverters (ms)

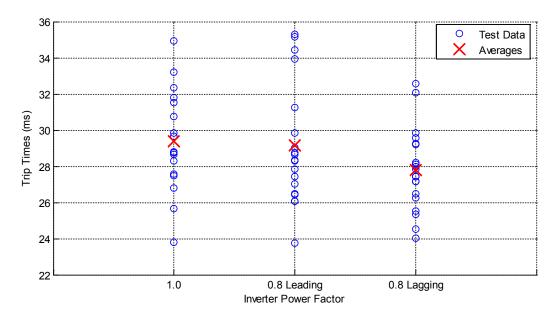

Individual plots of all test points and average trip times as a function of power factor are shown in Figure 14 through Figure 16. The binary behavior of Inverter 2 is evident: it has both the longest and the shortest trips times of the three inverters. Its behavior depends on the magnitude of the initial voltage spike due to the fault current, with large voltage spikes producing rapid shutdown and smaller spikes often leading to longer run-on time. Note that the longer run-on times would likely not occur in real-world scenarios without the balanced load:generation ratio required by the test plan. Nevertheless these run-on times are all under 12 line cycles and are not concerning given the near-nominal voltage levels. The trip times of Inverters 1 and 3 were more predictable and were always under 3 line cycles.

<sup>&</sup>lt;sup>9</sup> The generator reference frame is used in this report: lagging power factor corresponds to sourcing reactive power, and leading power factor corresponds to sinking reactive power.

Figure 14: Trip time as a function of power factor for Inverter 1

Figure 15: Trip time as a function of power factor for Inverter 2

Figure 16: Trip time as a function of power factor for Inverter 3

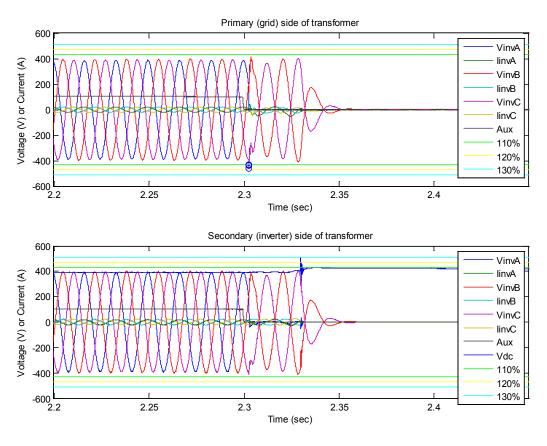

### 3.6 Waveforms of Interest

This section shows a selection of waveforms showing inverter behavior during the ground fault event for each of the test inverters. Each inverter had unique responses to the fault event, but the responses can be grouped into similar and repeatable response types. This section contains some waveforms that are considered typical inverter responses, along with others that had a unique or outlying response. This section is not meant to be an exhaustive report on all waveform characteristics, but instead is meant to provide insights into the differences between inverter responses. In general, GFO test results were much more consistent and contained fewer outliers than LRO test results presented in [4]. This section also presents plots of symmetrical component for selected tests to provide insight into the effect grounding transformers would have on the inverter ground fault responses.

Each waveform plot shows the AC terminal voltages, inverter current, DC bus voltage, and the auxiliary contact signal (labeled "Aux") showing when switch S2 closed, creating the fault (see Figure 1). The closing of switch S2 actually occurs 2-4 ms after Aux goes low, as is clear from the abrupt change in the faulted phase voltage in many plots. Note that trip times presented above are measured from the actual fault time rather than from the time the Aux signal goes low. Each plot also has horizontal lines showing the 110%, 120%, and 130% voltage threshold levels (when necessary). The interval of time where the maximum continuous overvoltage at each voltage threshold occurs is highlighted in each waveform. The alphanumeric name given in parentheses in each waveform caption corresponds to the raw data file name.

This section also presents unintentional islanding test waveforms for Inverters 2 and 3, which were primarily tested using test Version 2. These AI tests serve as baselines for the GFO tests under Version 2, which initiates the ground fault immediately following the creation of the island.

#### **Inverter 1 Waveforms**

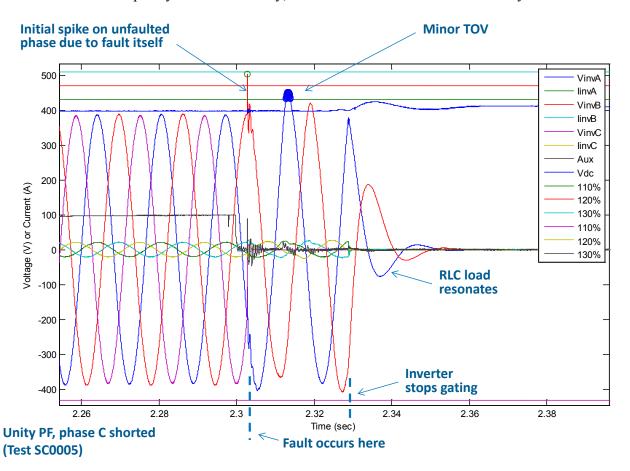

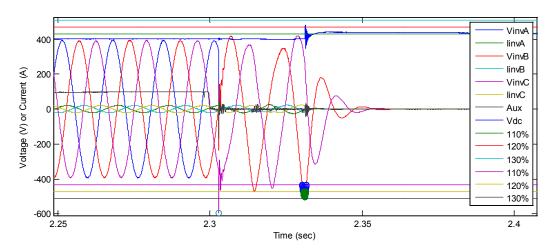

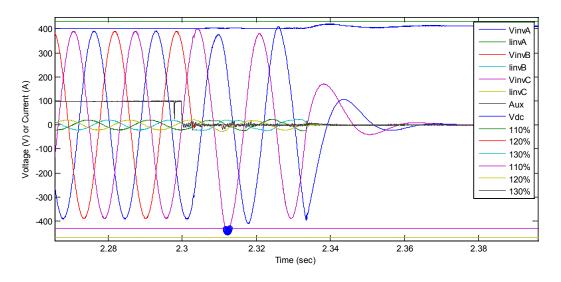

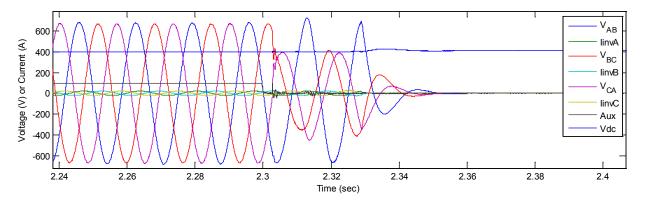

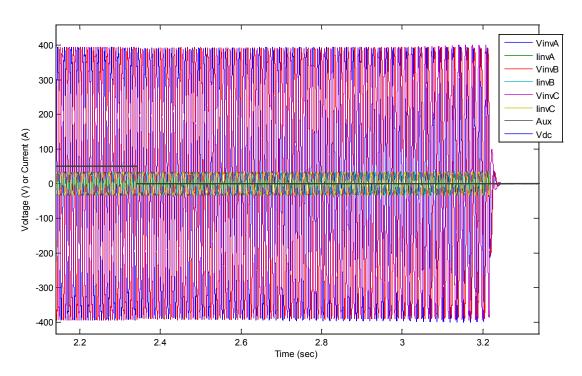

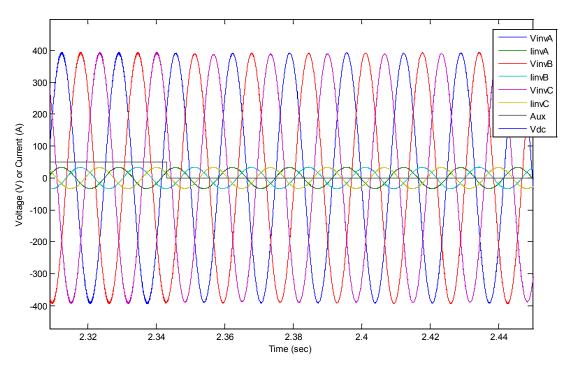

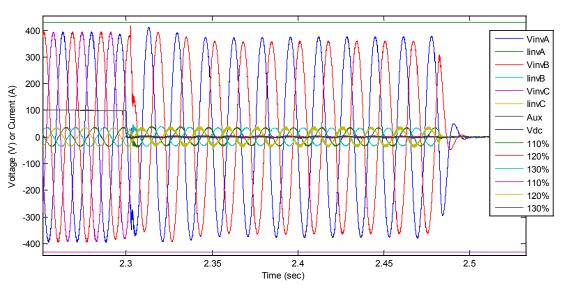

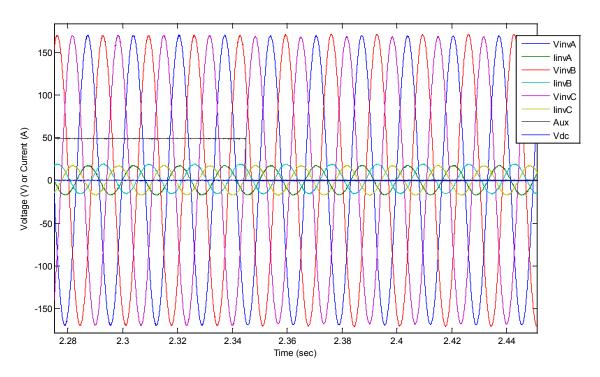

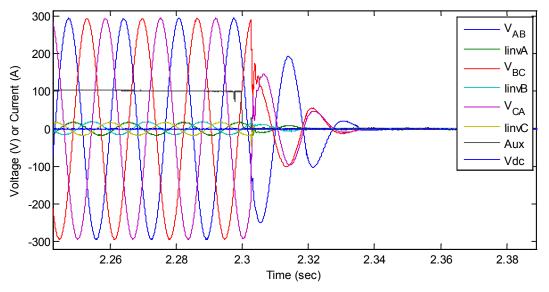

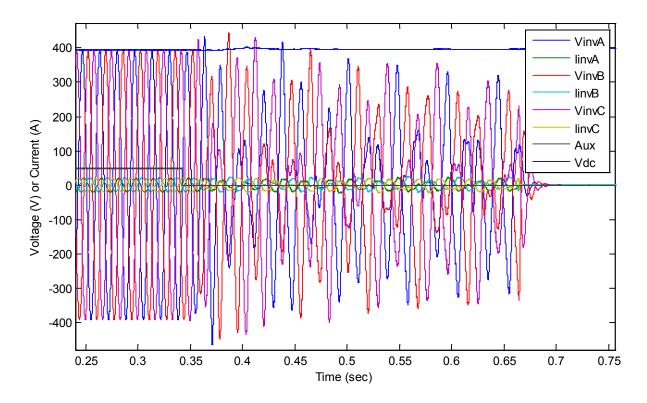

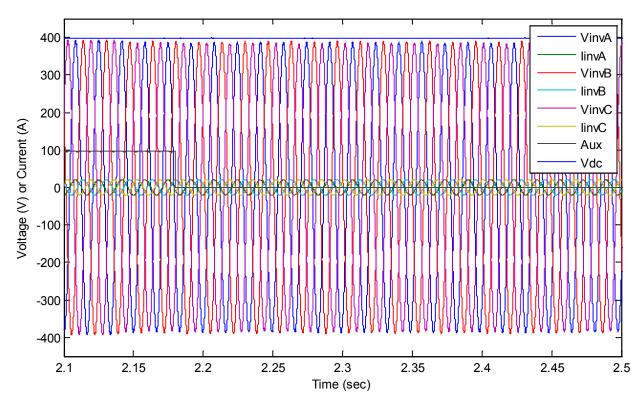

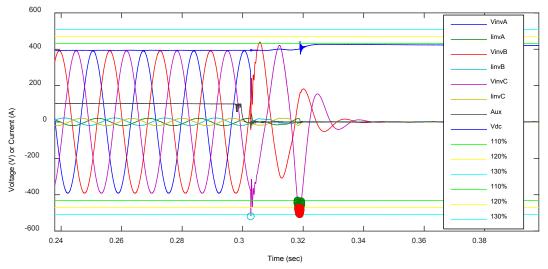

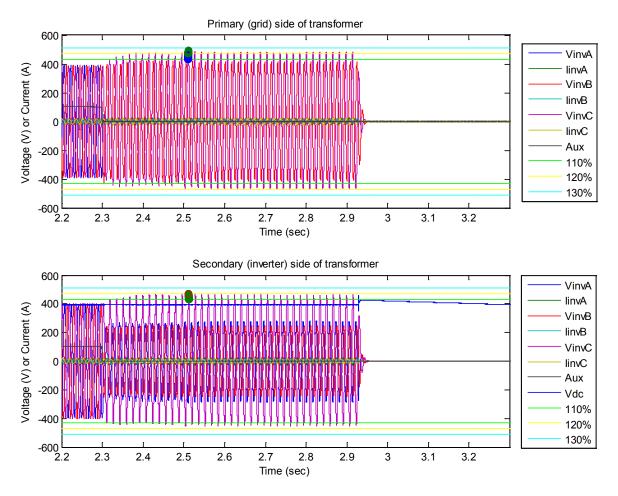

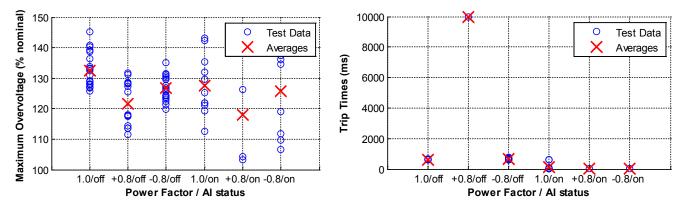

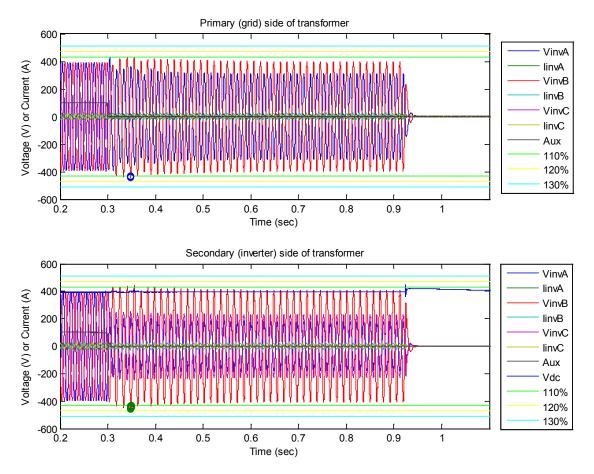

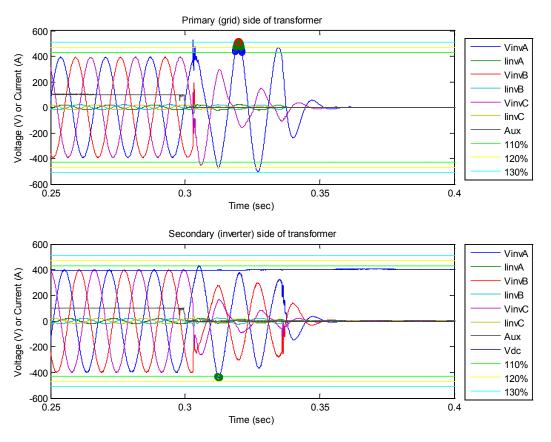

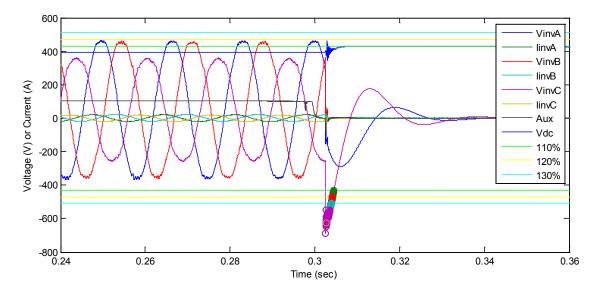

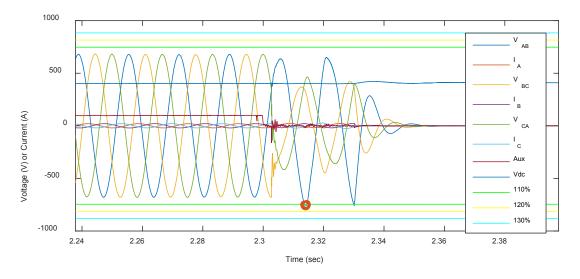

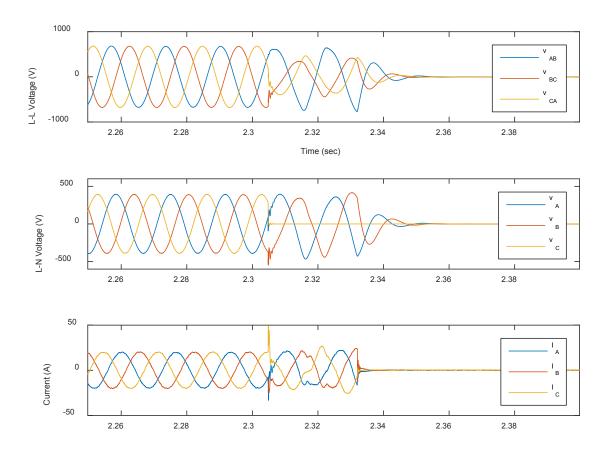

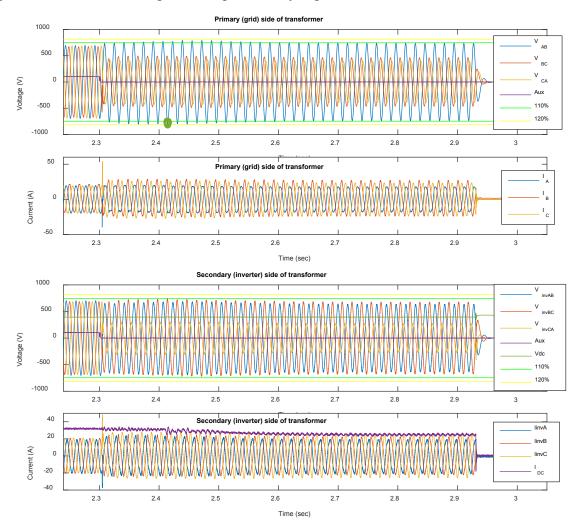

Figure 17 shows a typical response of Inverter 1 with annotations to point out salient features. For this test the inverter was operating at unity power factor and the fault occurred on phase C. At the time of the fault (just after 2.3 s), the faulted phase voltage, which was negative, went immediately to near zero, and the other two phase voltages rose by nearly the same amount. This created a significant but very brief overvoltage on phase B, which was near its peak. After the brief spike, all three inverter currents returned to nearly nominal-magnitude sinusoids with noticeable harmonics, and the two unfaulted phase voltages continued on sinusoidal trajectories with noticeable unbalance. This unbalance led to some overvoltage on phase A at the 110% level, but only on the positive half of the sinusoid. There was no overvoltage on the other phase. After about two AC cycles, the inverter stopped gating, evidenced by the abrupt cutoff of current around 2.33 s. The unfaulted phase voltages displayed a decaying resonance at 60 Hz after the inverter stopped exporting current. This resonance was driven by the RLC load, and as expected for a circuit with quality factor near unity, the resonance lasts about one line cycle.

Figure 17: Inverter 1 waveform at unity power factor (test SC0005)

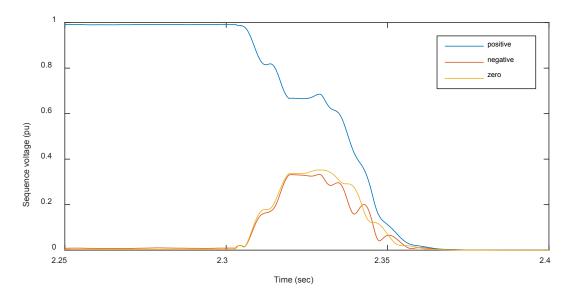

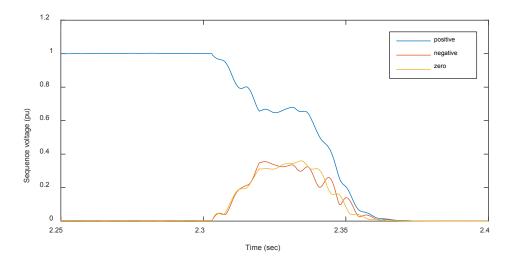

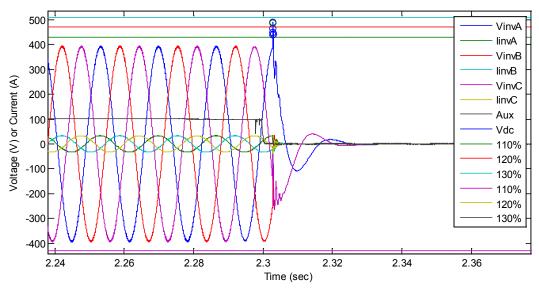

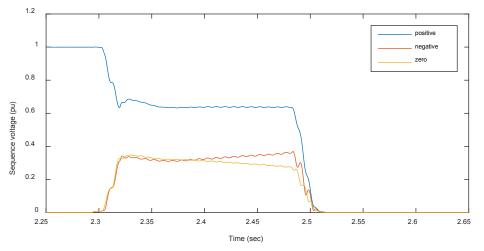

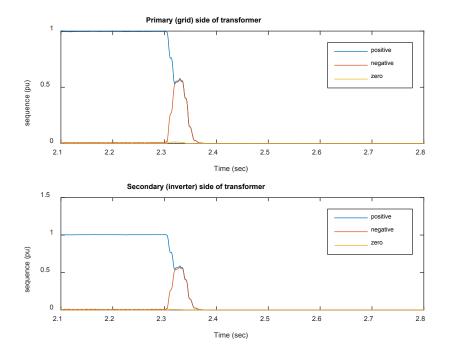

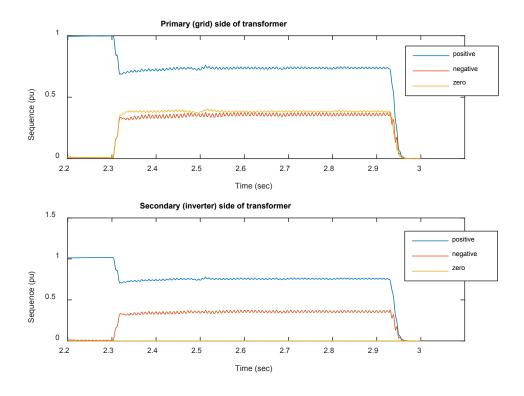

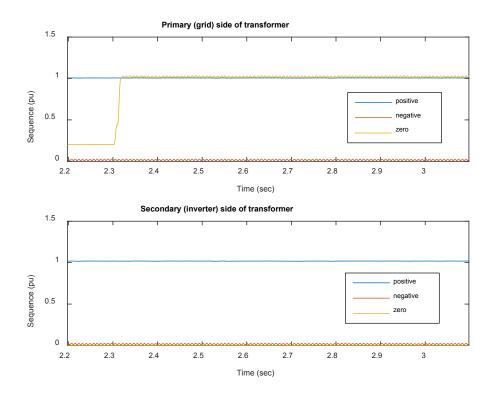

Figure 18 shows the symmetrical component magnitudes of the voltage waveforms in Figure 17. The positive sequence component drops from 1.0 pu (per unit) before the fault to about 0.7 pu for the two line cycles following the fault before the inverter disconnects. During those two line cycles, both the negative and the zero sequence components rise from near zero to about 0.35 pu.

In the "traditional" GFOV mechanism normally associated with synchronous machines (derived neutral point shift), nearly all of the unbalanced voltage would appear in the zero sequence. The split between negative and zero sequences seen in Figure 18 indicates that this unbalance is not caused by a derived neutral point shift.

Figure 18: Symmetrical components of Inverter 1 voltage waveforms at unity power factor (test SC0005)

Both the waveforms and the symmetrical components in this response were fairly typical for this inverter regardless of power factor and faulted phase. The magnitude of the brief overvoltage spike at the time of the fault varied depending on the voltages of the faulted and unfaulted phases at the time of the fault, and the exact shape of the voltage waveforms varied as well.

Note that all of the highest overvoltages recorded in the sections above (for all three inverters) were due to the brief initial spike at the time of the fault, and not to sinusoidal overvoltages typically associated with GFO. In a real feeder ground fault scenario the grid source is still present during the initial ground fault, so this spike would typically be driven by a combination of grid-sourced current and current sourced by any inverters connected to the feeder. The longest *duration* overvoltages are due to sinusoidal overvoltage, but the magnitudes of sinusoidal overvoltage are consistently low.

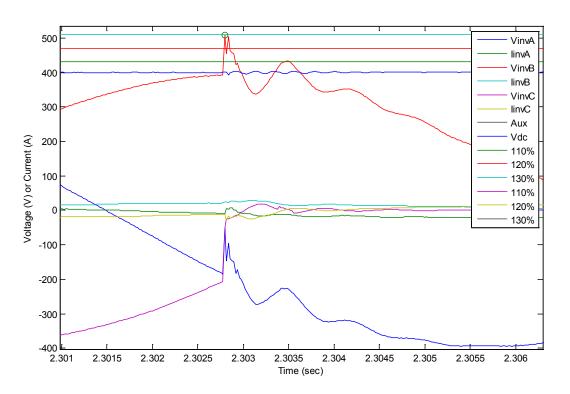

It is worthwhile to examine the fault voltage spike briefly. Figure 19 shows a zoomed in view of the spike. When phase C was shorted, its voltage rose nearly 200 V in one sample period (20  $\mu$ s). Phases A and B both rose by roughly 100 V in the same time. This indicates that a large ground fault current flowing through the very small neutral-to-ground impedance caused a very brief drop in the neutral voltage of roughly 100 V – the neutral point essentially met phase C halfway, ending up 100 V below ground potential, temporarily. So, while the voltages relative to earth ground on phases A and B likely changed very little, the phase-neutral voltages  $V_{AN}$  and  $V_{BN}$ , which are what was measured, both changed by 100 V. In the case of phase A, which was already negative,  $V_{AN}$  simply became less negative. But in the case of phase B, which was positive and near its peak, the voltage  $V_{BN}$  suddenly spiked by 100 V. This spike died out fairly quickly (with some ringing) as the fault current decayed.

It is worth noting that in this experimental setup only a few meters of cable separated the inverter from the fault location, so the impedance between the fault and the inverter is very low. In a typical field ground fault, there would be higher impedance between the inverter and the fault (and the grid itself would also typically still be connected during the fault). So the fault voltage spikes recorded here should not be taken to be representative of field conditions, which would likely see lower fault current contributions from the inverter.

This is significant because it shows that the initial spike is partially attributable to the fault itself, rather than to the inverter, though the inverter does source some of the fault current, with the rest coming from the resonant load itself. The fact that some of the fault current comes from the load explains why lagging power factor tests tended to have higher voltage spikes: at lagging power factor the parallel RLC load contains more inductance and less capacitance, and hence has higher impedance at very high frequencies. This higher impedance leads to a larger voltage difference between the unfaulted phases and neutral.