# An Advanced Platform for Development and Evaluation of Grid Interconnection Systems using Hardware-in-the-Loop: Part III – Grid Interconnection System Evaluator

## **Preprint**

Blake Lundstrom, Mariko Shirazi, Michael Coddington, and Benjamin Kroposki

To be presented at the IEEE Green Technologies Conference Denver, Colorado April 4-5, 2013

NREL is a national laboratory of the U.S. Department of Energy, Office of Energy Efficiency & Renewable Energy, operated by the Alliance for Sustainable Energy, LLC.

Conference Paper NREL/CP-5500-57556 January 2013

Contract No. DE-AC36-08GO28308

### NOTICE

The submitted manuscript has been offered by an employee of the Alliance for Sustainable Energy, LLC (Alliance), a contractor of the US Government under Contract No. DE-AC36-08GO28308. Accordingly, the US Government and Alliance retain a nonexclusive royalty-free license to publish or reproduce the published form of this contribution, or allow others to do so, for US Government purposes.

This report was prepared as an account of work sponsored by an agency of the United States government. Neither the United States government nor any agency thereof, nor any of their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States government or any agency thereof.

Available electronically at <a href="http://www.osti.gov/bridge">http://www.osti.gov/bridge</a>

Available for a processing fee to U.S. Department of Energy and its contractors, in paper, from:

U.S. Department of Energy Office of Scientific and Technical Information P.O. Box 62 Oak Ridge, TN 37831-0062 phone: 865.576.8401

fax: 865.576.5728

email: mailto:reports@adonis.osti.gov

Available for sale to the public, in paper, from:

U.S. Department of Commerce National Technical Information Service 5285 Port Royal Road Springfield, VA 22161 phone: 800.553.6847

fax: 703.605.6900

email: orders@ntis.fedworld.gov

online ordering: <a href="http://www.ntis.gov/help/ordermethods.aspx">http://www.ntis.gov/help/ordermethods.aspx</a>

Cover Photos: (left to right) PIX 16416, PIX 17423, PIX 16560, PIX 17613, PIX 17436, PIX 17721

## An Advanced Platform for Development and Evaluation of Grid Interconnection Systems Using Hardware-in-the-Loop:

Part III—Grid Interconnection System Evaluator

Blake Lundstrom, Mariko Shirazi, Michael Coddington, Benjamin Kroposki National Renewable Energy Laboratory Golden, Colorado, U.S.A. blake.lundstrom@nrel.gov

Abstract—The world's energy paradigm continues to undergo a rapid shift towards an increased use of renewable energy sources. To support this shift, an advanced electric power system architecture is being implemented by many electric utilities, interconnected with new distributed energy resources. As these new installations occur, it is essential to verify that their grid interconnection systems (ICS) conform to the relevant grid interconnection standards and that they perform satisfactorily under a variety of variable resource input and grid output conditions. This paper describes a Grid Interconnection System Evaluator (GISE) that leverages hardware-in-the-loop (HIL) techniques to rapidly evaluate interconnection standard conformance of an ICS according to the procedures in IEEE Std 1547.1TM. The architecture and test sequencing of this evaluation tool, along with a set of representative ICS test results from three different photovoltaic (PV) inverters, are presented. The GISE adds to the National Renewable Energy Laboratory's (NREL) evaluation platform that now allows for rapid development of ICS control algorithms using controller HIL (CHIL) techniques, the ability to test the dc input characteristics of PV-based ICSs through the use of a PV simulator capable of simulating real-world dynamics using power HIL (PHIL), and evaluation of the grid interconnection conformance of an ICS.

Index Terms—distributed energy resources, grid interconnection, hardware-in-the-loop (HIL), IEEE Std 1547 $^{\rm TM}$ , interconnection standards.

### I. INTRODUCTION

### A. Background

The world's energy paradigm continues to undergo a rapid shift towards an increased use of renewable energy sources. Worldwide, 71 countries have renewable portfolio standards or other quotas mandating that their electric utilities produce a portion of their total energy from renewable sources [1]. The effect of these quotas is evident; investments in new renewable capacity and renewable power capacity worldwide have increased over 150% from 2009 to 2011 alone [1]. The U.S. Department of Energy's (DOE) Energy Information Administration predicts that this trend of growing renewable

power capacity will continue at least through 2035 [2]. At the same time, an advanced electric power system (EPS) architecture, including increasing amounts of distributed resources, load control, bi-directional power flow, advanced metering, and improved communications is gaining attention and being implemented by many electric utilities. This new EPS architecture further enables consumer participation and assists utilities in efficiently accommodating various distributed resources (DRs), such as PV, wind, fuel cell, micro turbine, and energy storage technologies.

In support of this shifting energy paradigm and new EPS architecture, a swiftly increasing number of renewable energybased DR installations are occurring, the majority at the EPS distribution system level. As these installations occur, it is essential to ensure that these systems, each of which interface to the EPS using a grid ICS, are properly interconnected with the EPS according to the relevant U.S. standards, which are UL 1741 [3] and IEEE Std 1547 [4]. However, grid interconnection conformance is not the only essential aspect of determining the performance of an ICS; the device's performance under variable resource input and grid output conditions is also important. To this end, NREL has been developing a platform for ICS evaluation using HIL. The first portion of this platform is introduced in [5]. This paper describes an addition to this platform—a grid interconnection system evaluator (GISE). The ground work for this concept was established in a previous NREL effort [6][7] and an initial version was described as a Grid Interconnection Evaluator [5]. This initial version was then renamed and improved upon to create the GISE, a fullyintegrated tool with a unified user interface for grid interconnection evaluation tests.

### B. IEEE Std 1547 and EPS Interconnection Conformance Testing

IEEE Std 1547, which was harmonized with UL 1741, was developed to provide a standard set of requirements surrounding issues such as voltage regulation, synchronization and isolation, response to abnormal grid conditions, power quality, and islanding for interconnecting ICS with the EPS. IEEE Std 1547.1 [8], *IEEE Standard Conformance Test*

Procedures for Equipment Interconnecting Distributed Resources with Electric Power Systems, provides a comprehensive set of test procedures for use in determining if a particular ICS meets the requirements of IEEE Std 1547. When following the step-by-step procedures in IEEE 1547.1, it becomes clear that the process of testing an ICS against IEEE Std 1547 is guite comprehensive and can become very timeconsuming. For example, when verifying that an ICS disconnects properly in the event of grid overvoltage or undervoltage conditions, the test must be repeated five times. If the ICS is a multi-phase device, the test must be repeated five times for each phase and then five times for all phases simultaneously. Furthermore, if the device has adjustable limits, the test must be repeated five more times at the maximum, minimum, and mid-point limit settings. Thus, there is significant potential to greatly reduce the amount of time required for running these conformance tests by automating portions of the test procedures using HIL simulation techniques.

### C. HIL and Automated EPS Interconnection Conformance Testing

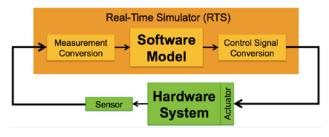

HIL simulation is a technique by which hardware systems and software models can be placed together into a single closed-loop simulation. This is accomplished by using a realtime simulator (RTS) that runs the software model and the communication interface between software and hardware deterministically and in actual time (see Fig. 1.). In doing so, outputs from the hardware system (e.g., output current in the case of an ICS) can be measured and converted to a digital value. These digital values used as inputs to a software model and outputs calculated, and these digital outputs converted to analog outputs (e.g., inverter gate drive signals, breaker control, grid simulator control signal, etc. depending on the application) that are sent to the hardware system, all in one time step. The period of this simulation time step is adjustable, but must be long enough that the computation required for the process detailed above can complete and short enough that the software model can respond faster than any output dynamics of the hardware system, and so that the software model accurately reflects the dynamics of the physical system it is simulating.

Fig. 1. Typical HIL Simulation Setup

HIL simulation allows for rapid development of any portion of a closed-loop control system, whether it is based in hardware, software, or both. For example, earlier work on the NREL ICS development and evaluation platform [5] included both a CHIL-based methodology, by which ICS controllers can be tested against simulated inverter hardware prior to at power

testing, and a PHIL-based PV simulator that can be used to test a PV ICS response to the truly dynamic output of a PV array. A number of other projects have leveraged CHIL and PHIL techniques for use with motor drives [9], generator excitation systems [10], and renewable energy applications [11], [12]. The use of HIL for grid conformance testing is mentioned in [13] and [14], however both of these works simply mention concepts and methodologies for testing different grid conformance aspects and lack implementation and results. In the case of the GISE described in this paper, HIL simulation techniques are used to considerably shorten the amount of time required to complete a full set of grid interconnection conformance tests by placing a software control model of each conformance test in the loop with the ICS under test and the related electrical test equipment.

### D. HIL and Advanced ICS Development and Evaluation

The existing standards for interconnection with the EPS in the United States, as detailed in IEEE Std 1547, were first collaborated on in 1999 and then published in 2003. Since that time, significant advancement of the grid support capabilities of ICSs, especially power electronics-based ICSs, has occurred. These new devices can be particularly valuable to the power system in providing advanced grid functions such as voltage ride-through (VRT) and/or frequency ride-through (FRT), volt/var control, or other ancillary services. However, because of these new grid support capabilities, these advanced ICSs don't necessarily comply with the recommended limits indicated in IEEE Std 1547 and thus some electric utilities are hesitant to allow their installation. An amendment to IEEE Std 1547 (P1547a), which is tasked with addressing some of these discrepancies, is underway, but until that time it is particularly useful to perform PHIL-based tests that evaluate how a particular advanced ICS will operate in a particular local EPS. Such simulations are accomplished by using a software model of the local area EPS which is then coupled to a simulated EPS point of common coupling, where the actual ICS hardware is connected. This capability was demonstrated in a related DOE/NREL project [15] and provides an excellent addition to the platform described in this paper, allowing for evaluation of a range of ICS that may or may not have advanced grid support functions or conform to the recommended limits of IEEE Std 1547.

### II. GISE REALIZATION

### A. Overview

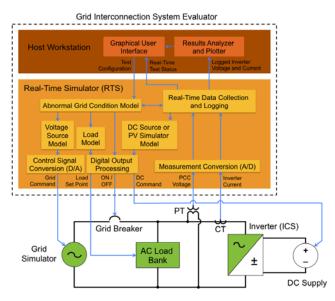

The complete architecture of the GISE is shown in Fig. 2. It can be seen that the GISE is comprised of four major sections:

- 1. Electrical hardware setup

- 2. RTS and models

- 3. Results analyzer and plotter

- 4. Graphical user interface.

This section will provide further detail on these four components.

Fig. 2. Grid Interconnection System Evaluator Architecture

### B. Electrical Hardware Setup

The GISE's electrical hardware setup is shown in the test circuit at the bottom of Fig. 2. In this test circuit, the grid simulator and grid breaker function as the simulated EPS point of common coupling, the ac load bank as the constant resistive or resonant RLC load (depending on test), and the dc supply as the DR being interconnected through the inverter ICS.

Specifically, the following electrical equipment was used for the tests described in this paper:

- **Grid simulator**: 62.5 kVA (four units for up to 250 kVA available) voltage source configured for output in a 240 V<sub>rms</sub> nominal, split-phase configuration in response to a line voltage waveform command. This unit will maintain output frequency within 0.01% and will regulate individual phase voltages within 0.5%. It has a frequency range of 47 to 500 Hz, a voltage range of 0 to 132 VL-N (before a step-up output transformer), and a slew rate of 1 V/μs. The analog control of this grid simulator, which is operated from the voltage source model running on the RTS, is very fast with response times of 300 μs for 100% load changes.

- Grid breaker: LSI molded case circuit breaker, 400A frame, electronic trip, with shunt trip and auxiliary contacts for status

- AC load bank: 436 kVA @ +/- 0.37 pf with 125 W and 312.5 VAR steps

- **DC supply**: 250 kW, 0-900 VDC

- Inverter (ICS): a variety of commercial maximum power point tracking (MPPT) PV inverters rated for approximately 3 kW of power transfer capacity

- **Potential transformer (PT)**: 40:1 turns ratio

- Current transducer (CT): 10 mV/A, 10 kHz bandwidth

### C. RTS and Models

### 1) Real-Time Simulator

The real-time simulator provides the key interface between the physical electrical components and the software models that control them. The physical simulator used for the testing described in this paper is an eMegaSim Wanda 4U model [16] from Opal-RT Technologies. The complete RTS model is developed using MATLAB Simulink, compiled into executable code using Mathworks' Real-Time Workshop, and deployed onto the RTS using Opal-RT's RT-LAB. Each of the individual key software models is described in the following sections.

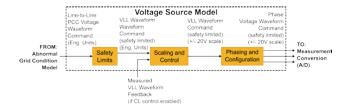

### 2) Voltage Source Model

The voltage source model is shown in Fig. 3. This model is simple with only three key subsystems:

- 1. Safety Limits limits the magnitude of the commanded waveform to ensure it is within the specified operating limits of the physical hardware.

- 2. Scaling and Control scales the voltage command given in engineering units to an analog voltage range understood by the grid simulator's internal controller; performs open-loop proportional or closed-loop proportional integral control on this scaled control signal depending on which method is enabled. By default, open-loop proportional control is used.

- 3. Phasing and Configuration depending on how the ICS is electrically connected to the grid simulator, different phase voltage waveform commands are generated. By default, a split-phase configuration is used and the ICS under test is connected across phase A and phase B of a three-phase power system bus. Thus, phase A and phase B are enabled and 180 degrees out of phase with one another, and phase C is disabled.

Fig. 3. Voltage Source Model

### 3) Load Model

The ac load bank used for this testing is governed by an onboard controller that opens and closes relays and switches to connect or disconnect the various R, L, and C elements to/from the physical power connections. The onboard controller must be commanded as to which relays to open or close by the RTS load model. Thus, the RTS load model interprets a user set point that includes the nominal voltage range (240 V or 480 V), the desired apparent power value in kVA, and the desired power factor, and, using knowledge of the available element combinations in the load bank, translates this set point into discrete on or off signals for all of the element relays and switches in the load bank. For example, when a set point of 22 kVA at pf = 0.707 lagging (this is equivalent to a resistive load

of 15.554 kW and an inductively reactive load of 15.554 kVAR) and 240 V is commanded, the relays corresponding to 240 V operation, a 15 kW resistor, a 500 W resistor, a 15 kVAR inductor, and a 312.5 VAR inductor would be commanded to be turned on and all other relays turned off. This set of relays is selected because, given the discrete resistive and inductive steps available, 15.5 kW and 15.3125 kVAR are the closest values that are less than or equal to the commanded values of 15.554 kW and 15.554 kVAR. The relay states are then digitally communicated to the load bank's onboard controller for execution.

### 4) DC Source or PV Simulator Model

The dc power source used for this testing is governed via an on-board controller that manages the source's internal ac inverter unit and dc converter unit to affect the desired power transfer and voltage characteristics on both channels of the source. This controller accepts set points for the source's limits and commanded operating conditions and communicates measured power transfer and voltage information for each channel via controller area network (CAN) digital communication. The RTS communicates via CAN with the dc power source controller to transfer these set points and measurements back and forth.

Within the RTS, a software model of either a dc source or a PV simulator is used to interpret measurements and provide set points. The dc source model takes a set point command input and then issues set points to the dc source in order to control the source's output to this commanded set point. The dc source model also reports measurements of the actual source's reported power transfer characteristics.

The PV simulator, the architecture of which is shown in [5], leverages this simple dc source model by using its reported measurements, an internal model of a PV array, and a basic control system to provide the dc source model commands so that the dc source behaves as an actual photovoltaic array would. This PV model includes both response to varying environmental—solar irradiance and cell temperature—input conditions and dc output power transfer characteristics (e.g., appropriate voltage, current, and power output corresponding to each loading scenario). Further detail on the PV simulator is given in [5].

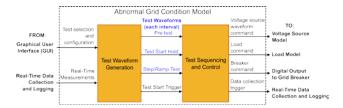

### 5) Abnormal Grid Condition Model

The abnormal grid condition model, a block diagram of which is shown in Fig. 4. below, is the core model of the GISE. This model contains two key subsystems:

- Test Waveform Generation generates the test waveforms for each of the three test intervals and a trigger signal depending on the user's test selection and configuration

- Test Sequencing and Control controls the overall timing of the test, ramps up and ramps down the overall test waveform, and sequences the three interval test waveforms so that they are executed at the correct times and there are no discontinuities between intervals. It

sends the reference command to the voltage source model, load model, and grid breaker.

Fig. 4. Abnormal Grid Condition Model

### D. Results Analyzer and Plotter

The Results Analyzer and Plotter is a set of scripts implemented in MATLAB that analyze the raw data collected by the RTS and calculate a number of key parameters or waveforms:

- 1. Time series of voltage magnitude (RMS) values over the test duration calculated on a full-cycle basis based on zero crossings

- 2. Time series of current magnitude (RMS) values over the test duration calculated using the last full cycle of the current waveform data, as determined by zero crossing detection

- 3. Time series of voltage frequency (Hz) values over the test duration calculated using the immediately previous two zero crossings (one full cycle)

- 4. Voltage and frequency magnitudes immediately prior to the start of the three test intervals (test intervals are described in section III) useful for verifying that the values specified in the test configuration are being properly commanded and in determining the actual step or ramp value that was commanded for a particular test

- 5. Exact time and magnitude at which the ICS disconnected during the ramp/step test interval (test intervals are described in section III) the key parameter being measured for all tests. The time at which the ICS disconnected is calculated based on when the current waveform first deviates from its periodic waveform towards zero (a complex algorithm examining first and second derivatives of the current is employed to determine this). This value and the point in time at which the ramp/step test interval began are then used to calculate the ICS's trip time. The magnitude at which the ICS disconnected is calculated based on the full cycle immediately previous to disconnection.

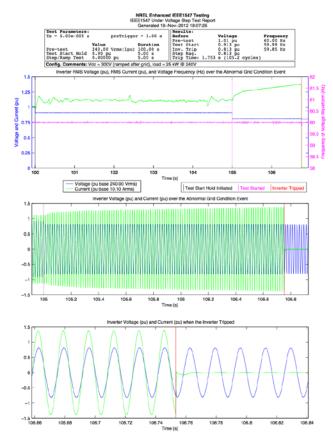

These key parameters are then used to generate a summary test report. An example summary test report from an undervoltage time interconnection conformance test is shown in Fig. 5. There are four key sections to this report:

Report Header – shows a tabular summary of the user's specified parameters (left) and the relevant results (right) for the test. The results table varies slightly depending on the test being run; the results table includes the measured ramp slope for magnitude/ramp tests and the measured step magnitude for time/step tests. This section is useful in quickly determining whether the ICS passed the test in question.

- 2. Top Plot this plot shows RMS values of the ICS's current and voltage magnitude, in addition to the frequency of the voltage waveform, as a function of time over the course of the entire test. The three test intervals (pre-test, test start hold, and ramp/step test; further explained in section III) are delineated by the vertical lines.

- Middle Plot shows the ICS current and voltage waveforms over the course of the entire test. This plot adds additional detail to the top plot in that one can better spot any periodic abnormalities in current output from the waveform.

- 4. **Bottom Plot** shows the ICS current and voltage waveforms just before and after the inverter tripped. This plot is most useful for determining what the ICS's current waveform looked like right as it tripped.

For every test that is run, a summary test report of this same format is generated. The raw data for each test is also saved and available for further examination offline.

Fig. 5. Example Summary Test Report for an Undervoltage Time/Step Test

### E. Graphical User Interface

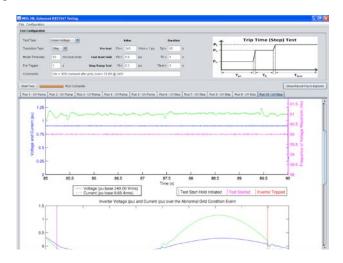

Fig. 6. shows a screenshot of the graphical user interface (GUI), from which a user can configure, run, monitor, and view results of grid interconnection conformance tests.

Configuration takes place at the top of the screen where the user selects the desired tests, enters the relevant parameters, and enters a comment if desired. A graphic at right assists the user with understanding the parameters being entered as they relate to the selected test. Once configured, the user presses "Start Test," which will verify that the entered parameters are valid and then execute the test using the RTS.

Upon test completion, the GUI collects the test data logged by the RTS over the entire test and sends that to the results analyzer and plotter. Once analysis is finished, a new results tab with the generated report (see Fig. 5. for an example) is opened at the bottom of the screen. All results of the test are available in this PDF report, and raw data is also saved. More detail about the configuration and sequence of specific tests is given in section III below.

Fig. 6. Graphical User Interface

### III. GISE TEST CONFIGURATION AND SEQUENCE

Successfully executing a grid interconnection conformance test using the GISE consists of the following steps:

- 1. Equipment Setup the user connects and configures the ICS under test and the relevant electrical equipment as shown in Fig. 2. while following the relevant manufacturer guidance and taking proper safety precautions.

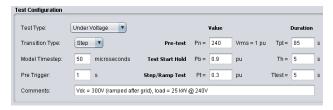

- **2. Test Configuration** using the Test Configuration portion of the GUI, a zoomed-in view of which is shown in Fig. 7. , the user specifies:

- Test Type:

- Overvoltage (OV)

- Undervoltage (UV)

- Overfrequency (OF)

- Underfrequency (UF)

- Unintentional Islanding (UI)

- Transition Type (only applicable for OV, UV, OF, or UF tests):

- Step/Time measures the amount of time required by the ICS to respond to and disconnect after an abnormal grid condition is detected

- Ramp/Magnitude measures the voltage or frequency magnitude at which the ICS disconnected

- Model Timestep defines how fast the model runs and thus how fast data collection occurs. The default value of 50 microseconds is generally sufficient. The user is allowed to enter values between 10 and 100 microseconds.

- Pre Trigger amount of time in seconds before the Test Start Hold interval begins to log test data. Data is logged from the start of the test minus the pre trigger until the end of the test. The user is allowed to enter values between 0.01 and 10 seconds, though the default of 1 second is recommended.

- Nominal parameter (voltage or frequency) magnitude and interval duration for the three intervals during testing:

- Pre-test used to allow the inverter to wake-up, synchronize, etc. Explained to the user when entering this value into the GUI (see graph at top right in Fig. 6. The value is specified in units of V<sub>rms</sub> and the duration is specified in seconds.

- Test Start Hold temporary period immediately before test occurs during which the starting parameter value (P<sub>b</sub>) is held for duration T<sub>h</sub>. Explained to the user when entering this value into the GUI (see graph at top right in Fig. 6. Value is specified in per unit (pu) for voltage tests and Hertz (Hz) for frequency tests. Duration is specified in seconds.

- Step/Ramp Test period during which the specified test occurs over the duration T<sub>test</sub>. The test parameter is either the desired value to step to (P<sub>t</sub>, for a time test) or the desired ramp rate (M<sub>ramp</sub>, for a magnitude test). Explained to the user when entering this value into the GUI (see graph at top right in Fig. 6. Value is specified in pu or pu/s for voltage tests and Hz or Hz/s for frequency tests. Duration is specified in seconds.

- Comments useful for noting any details about the test configuration of the particular ICS under test

Fig. 7. Test Configuration and Status Portion of the GUI

- 3. Parameter Verification and Test Execution once the user sets the configuration parameters above, the "Start Test" button is pushed. Upon this action, the specified parameters are then verified to ensure that they make sense given the selected test and transition type, are within the allowable ranges for each of the parameters, and won't cause any equipment to be commanded to an unsafe condition (e.g., too high a voltage or frequency commanded on the grid simulator). Next, the configuration is communicated to the RTS, which then builds its model and executes the test in three intervals. The user is apprised of real-time test status throughout the test via the GUI status progress bar and message shown at the bottom of the Test Configuration section. Fig. 7. shows the progress bar and message configuration that are displayed when a test is complete. In the middle of a test, varying status messages and progress bar completions are shown that tell the user when the RTS model is being built, being loaded, what interval of testing is occurring, if analysis after the test is being completed, or when the test is complete.

- 4. Results upon test completion, data collected throughout the test is passed from the RTS to the Results Analyzer and Plotter, where the result parameters are calculated and plots created. This information is then organized into a report, which is described in the next section, and displayed to user in the same GUI. The results from each test run are displayed in a new tab, as shown for 10 tests in Fig. 6., so that many test runs can be completed in a short succession and the results easily compared. The reports are automatically saved as a PDF document that can be located in the workstation's operating system by the Show Result File in Explorer button.

- 5. Repeat Steps 2-4 these steps are repeated for each additional test run. If the test configuration specified in step 2 doesn't change between test runs, the RTS model is not recompiled and the testing period begins immediately.

### IV. GISE TEST RESULTS

### A. Test Setup and Methodology

For demonstration of the GISE, three different commercial PV inverters were tested as the ICSs under test. These three inverters all had power transfer capability ratings of around 3 kW and were connected to the simulated Area EPS in a split-phase 240 V configuration. The grid simulator was operated using analog waveform control from the RTS voltage source model as described in section II.B. The ac load bank was given a constant load set point of 10 kW by the RTS load model for over- and undervoltage and frequency tests. For unintentional islanding tests, the load bank was manually tuned to resonant conditions via user interaction with the load model. For these tests, the dc power source was commanded by the RTS dc source model to operate in voltage control mode with a constant voltage appropriate for each inverter.

This testing sequence performed nine of the IEEE 1547.1 interconnection conformance tests (overvoltage time and magnitude, undervoltage time and magnitude, overfrequency time and magnitude, underfrequency time and magnitude, and unintentional islanding); however, for the sake of brevity, only two tests are shown and described in the following sections. The results presented were selected to show the GISE's functionality to perform these interconnection tests across a variety of ICS with varying topologies; they are not intended to be a complete (e.g., the appropriate number of repetitions) set of tests according to the procedures of IEEE Std 1547.1. Each set of tests is summarized using a table of results that describes the overall strategy and purpose of individual test runs, and a plot of multiple repeated identical test runs, which demonstrates the repeatability and accuracy of the GISE's execution of the test set and the slight variability in ICS output response for each test run. This plot has a very similar format to the example test report of Fig. 5. in that it shows the RMS voltage, the RMS current, and the calculated (on a full-cycle basis) frequency over the course of the test run's three intervals (delineated with vertical lines).

### B. Representative Tests

### 1) Overvoltage Magnitude Test

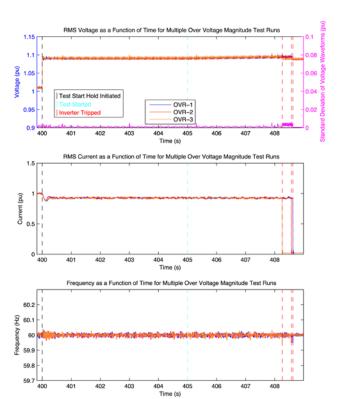

A selection of over voltage magnitude test results is given in TABLE I. The first three test runs were for identical configuration parameters and so results from these specific runs are shown in Fig. 8. to demonstrate the repeatability and accuracy of the GISE's execution of the test set and the slight variability in ICS output response for each test run. In examining Fig. 8., one will notice that the RMS voltages for the set of tests are all very similar as demonstrated by very low standard deviations.

TABLE I. SUMMARY OF SELECTED OVERVOLTAGE MAGNITUDE TESTS

| Test<br>Run # | PT Hold<br>Magnitude<br>P <sub>b</sub><br>(pu) | PT Hold<br>Duration<br>T <sub>h</sub><br>(s) | Ramp<br>Rate<br>M <sub>ramp</sub><br>(pu/s) | Trip<br>Magnitude<br>(pu) | Demonstrates                                                                            |  |

|---------------|------------------------------------------------|----------------------------------------------|---------------------------------------------|---------------------------|-----------------------------------------------------------------------------------------|--|

| OVR-1         | 1.08                                           | 5                                            | 0.001                                       | 1.096                     | -                                                                                       |  |

| OVR-2         | 1.08                                           | 5                                            | 0.001                                       | 1.097                     |                                                                                         |  |

| OVR-3         | 1.08                                           | 5                                            | 0.001                                       | 1.097                     | The slow over                                                                           |  |

| OVR-4         | 1.08                                           | 5                                            | 0.00272                                     | 1.1                       | voltage trip<br>magnitude of the<br>ICS, OVR-1 through<br>OVR-3 are shown in<br>Fig. 8. |  |

| OVR-5         | 1.08                                           | 5                                            | 0.001                                       | 1.098                     |                                                                                         |  |

| OVR-6         | 1.08                                           | 5                                            | 0.001                                       | 1.099                     |                                                                                         |  |

| OVR-7         | 1.08                                           | 5                                            | 0.001                                       | 1.097                     |                                                                                         |  |

| OVR-8         | 1.08                                           | 5                                            | 0.001                                       | 1.092                     |                                                                                         |  |

| OVR-9         | 1.18                                           | 0.32                                         | 0.00545                                     | 1.193                     |                                                                                         |  |

| OVR-10        | 1.18                                           | 0.32                                         | 0.00545                                     | 1.192                     | The feet !                                                                              |  |

| OVR-11        | 1.175                                          | 0.32                                         | 0.00545                                     | 1.187                     | The fast overvoltage<br>trip magnitude of the<br>ICS.                                   |  |

| OVR-12        | 1.175                                          | 0.32                                         | 0.00545                                     | 1.19                      |                                                                                         |  |

| OVR-13        | 1.175                                          | 0.32                                         | 0.00545                                     | 1.191                     |                                                                                         |  |

Fig. 8. Multiple Overvoltage Magnitude Test Runs

### 2) Overfrequency Magnitude Test

A selection of the under frequency time test results is given in TABLE II. Fig. 9. shows a plot of the first three of the test runs listed in TABLE II. to demonstrate the repeatability and accuracy of the GISE's execution of the test set and the slight variability in ICS output response for each test run. In examining Fig. 9., one will notice that the frequencies for the two sets of tests are nearly identical. This plot also shows that there are some oscillatory deviations in the currents for each run. These deviations are due to the fact that the inverters under test had MPPT control enabled, but were drawing power from the fixed dc source. Thus, the output current tended to hunt. This behavior was observed as normal for all inverters tested.

TABLE II. SUMMARY OF SELECTED UNDER FREQUENCY TIME TESTS

| Test<br>Run # | PT Hold<br>Magnitude<br>P <sub>b</sub><br>(Hz) | PT Hold<br>Duration<br>T <sub>h</sub><br>(s) | Test<br>Magnitude<br>P <sub>t</sub><br>(Hz) | Test Duration T <sub>test</sub> (s) | Trip<br>Time<br>(s) | Demonstrates                                                             |

|---------------|------------------------------------------------|----------------------------------------------|---------------------------------------------|-------------------------------------|---------------------|--------------------------------------------------------------------------|

| UFS-1         | 59.6                                           | 5                                            | 59                                          | 2                                   | 0.123               | The under<br>frequency trip<br>timing of the<br>ICS. Shown<br>in Fig. 9. |

| UFS-2         | 59.6                                           | 5                                            | 59                                          | 2                                   | 0.106               |                                                                          |

| UFS-3         | 59.6                                           | 5                                            | 59                                          | 2                                   | 0.102               |                                                                          |

| UFS-4         | 59.6                                           | 2                                            | 59                                          | 2                                   | 0.159               | The under frequency trip timing of the ICS at other test magnitudes.     |

| UFS-5         | 59.6                                           | 2                                            | 59                                          | 2                                   | 0.159               |                                                                          |

| UFS-6         | 59.6                                           | 5                                            | 58                                          | 2                                   | 0.106               |                                                                          |

| UFS-7         | 59.6                                           | 5                                            | 57                                          | 2                                   | 0.115               |                                                                          |

| UFS-8         | 59.6                                           | 5                                            | 57                                          | 2                                   | 0.107               |                                                                          |

Fig. 9. Multiple Underfrequency Time Tests

### V. CONCLUSIONS AND CONTINUING WORK

This paper describes and demonstrates a grid interconnection system evaluator that provides a method to vastly increase the efficiency of conducting IEEE Std 1547 and other grid interconnection conformance tests through the use of HIL simulation techniques, advanced analysis scripts, and a single user interface. Using the GISE's GUI, an operator can now configure, run, monitor, and view analyzed summary results for over/under voltage and frequency and unintentional islanding IEEE Std 1547 grid conformance tests from a single interface. The accuracy, repeatability, and applicability to various ICS with different internal topologies of the GISE test execution were also demonstrated.

More than just automating a test procedure, this work adds further capability to NREL's advanced platform for development and evaluation of grid interconnection systems. This platform now allows for rapid development of ICS control algorithms using CHIL techniques, the ability to test the dc input characteristics of PV-based ICS through the use of a PV simulator capable of simulating real-world dynamics using PHIL, and now evaluation of ICS grid interconnection conformance. This platform offers a unique set of capabilities that will help develop and evaluate the next generation of ICS that will be prevalent in future advanced EPS architectures.

Upcoming work will involve further developing methods to leverage PHIL techniques to advance unintentional islanding, VRT, FRT, and volt/var control testing capabilities, and

performing more realistic simulations of ICS interfaced at various local EPS PCCs.

### ACKNOWLEDGMENT

The authors would like to thank Kevin Lynn of DOE and Alvin Razon of SRA International for their support on this project. The lead author would also like to thank Dr. P.K. Sen of Colorado School of Mines for his advice on this project.

### REFERENCES

- [1] REN21, "Renewables 2012 Global Status Report," Paris, 2012.

- [2] US Energy Information Administration, "International Energy Outlook 2011," 2011.

- [3] Underwriters Laboratories, "UL 1741: Inverters, Converters, Controllers, and Interconnection System Equipment for Use with Distributed Energy Resources." 2007.

- [4] IEEE, "IEEE 1547-2003: IEEE Standard for Interconnecting Distributed Resources with Electric Power Systems." 2003.

- [5] B. Lundstrom, S. Chakraborty, B. Kramer, D. Terlip, and B. Kroposki, "An Advanced Platform for Development and Evaluation of Photovoltaic Inverters Using Hardware-in-the-Loop," *International Journal of Distributed Energy Resources and Smart Grids*, vol. 9, no. 1, Mar. 2013.

- [6] D. V. Terlip, B. Kroposki, and D. Maksimovic, "A methodology for characterizing and modeling inverters for grid integration studies using Power Hardware-in-the-Loop," presented at the 2012 IEEE Power and Energy Society General Meeting, San Diego, CA, 2012.

- [7] Daniel V. Terlip, "A Methodology for Characterizing and Modeling Inverters for Grid Integration Studies using Power Hardware-in-the-Loop," MS Thesis, University of Colorado at Boulder, Boulder, CO, 2011.

- [8] IEEE SCC21, "IEEE 1547.1: Standard Conformance Test Procedures for Equipment Interconnecting Distributed Resources with Electric Power Systems." 2005.

- [9] M. Steurer, C. Edrington, M. Sloderbeck, W. Ren, and J. Langston, "A Megawatt-Scale Power Hardware-in-the-Loop Simulation Setup for Motor Drives," *IEEE Trans. of Indus. Elec.*, vol. 57, no. 4, pp. 1254–1260, Apr. 2010.

- [10] K. Schoder, J. Langston, M. Steurer, S. Azongha, M. Sloderbeck, T. Chiocchio, C. Edrington, A. Farrell, J. Vaidya, and K. Yost, *Hardware-in-the-Loop Testing of a High-Speed Generator Excitation Controller*. Tallahassee: Florida State University CAPS, 2010.

- [11] M. Steurer, F. Bogdan, W. Ren, M. Sloderbeck, and S. Woodruff, "Controller and Power Hardware-in-the-Loop Methods for Accelerating Renewable Energy Integration," presented at the IEEE Power Energy Society General Meeting, 2007, pp. 1–4.

- [12] A. Monti, F. Ponci, Z. Jiang, and R. Dougal, "Hardware-in-the-Loop Testing Platform for Distributed Generation Systems," International Journal of Energy Technology and Policy, vol. 5, no. 2, pp. 241–257, 2007.

- [13] S. Suryanarayanan, W. Ren, M. Steurer, F. Ribeiro, and G. T. Heydt, "A Real-Time Controller Concept Demonstration for Distributed Generation Interconnection," presented at the Power Engineering Society General Meeting, 2006, p. 3.

- [14] P. Crolla, A. J. Roscoe, A. Dysko, and G. M. Burt, "Methodology for testing loss of mains detection algorithms for microgrids and distributed generation using real-time power hardware-in-the-loop based technique," presented at the 2011 IEEE 8th International Conference on Power Electronics and ECCE Asia (ICPE & ECCE), 2011, pp. 833–838.

- [15] J. Langston, K. Schoder, M. Steurer, O. Faruque, J. Hauer, F. Bogdan, R. Bravo, B. Mather, and F. Katiraei, "Power hardware-in-the-loop testing of a 500 kW photovoltaic array inverter," presented at the IECON 2012 38th Annual

- Conference on IEEE Industrial Electronics Society, 2012, pp. 4797–4802.

- [16] Opal-RT Technologies, "Wanda 4U," Dec-2012. [Online]. Available: http://www1.opal-rt.com/product/wanda-4u.