# 18<sup>th</sup> Workshop on Crystalline Silicon Solar Cells and Modules: Materials and Processes

# Workshop Proceedings

Workshop Chairman/Editor: B.L. Sopori

Program Committee: M. Al-Jassim, P. Basore, T. Buonassisi, J. Gee, J. Kalejs, B. Mulligan, J. Rand, T. Saitoh, R. Sinton, M. Stavola, T. Tan, E. Weber, J. Werner, and B. Sopori

Vail Cascade Resort Vail, Colorado August 3–6, 2008 Proceedings NREL/BK-520-45745 September 2008

# 18<sup>th</sup> Workshop on Crystalline Silicon Solar Cells and Modules: Materials and Processes

# Proceedings NREL/BK-520-45745 September 2008

**Workshop Proceedings**

Workshop Chairman/Editor: B.L. Sopori

M. Al-Jassim, P. Basore, T. Buonassisi, J. Gee, J. Kalejs, B. Mulligan, J. Rand, T. Saitoh, R. Sinton, M. Stavola, T. Tan, E. Weber, J. Werner, and B. Sopori

Vail Cascade Resort Vail, Colorado August 3–6, 2008

Prepared under Task No. WO97.J100

National Renewable Energy Laboratory 1617 Cole Boulevard, Golden, Colorado 80401-3393 303-275-3000 • www.nrel.gov

Operated for the U.S. Department of Energy Office of Energy Efficiency and Renewable Energy by Midwest Research Institute • Battelle

Contract No. DE-AC36-99-GO10337

#### NOTICE

Employees of the Midwest Research Institute under Contract No. DE-AC36-99GO10337 with the U.S. Dept. of Energy have authored this work. The United States Government retains and the publisher, by accepting the article for publication, acknowledges that the United States Government retains a non-exclusive, paid-up, irrevocable, worldwide license to publish or reproduce the published form of this work, or allow others to do so, for United States Government purposes.

This report was prepared as an account of work sponsored by an agency of the United States government. Neither the United States government nor any agency thereof, nor any of their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States government or any agency thereof.

Available electronically at http://www.osti.gov/bridge

Available for a processing fee to U.S. Department of Energy and its contractors, in paper, from: U.S. Department of Energy Office of Scientific and Technical Information P.O. Box 62 Oak Ridge, TN 37831-0062 phone: 865.576.8401 fax: 865.576.5728 email: mailto:reports@adonis.osti.gov

Available for sale to the public, in paper, from: U.S. Department of Commerce National Technical Information Service 5285 Port Royal Road Springfield, VA 22161 phone: 800.553.6847 fax: 703.605.6900 email: <u>orders@ntis.fedworld.gov</u> online ordering: <u>http://www.ntis.gov/ordering.htm</u>

# 18<sup>th</sup> Workshop on Crystalline Silicon Solar Cells & Modules: Materials and Processes

August 3 – 6, 2008 Vail, Colorado

#### TABLE OF CONTENTS

| Title/Author(s):                                                                                                                                   | Page |

|----------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Workshop Theme: "New Directions for Rapidly Growing Silicon Technologies" Bhushan Sopori                                                           | 1    |

| <b>Stimulating Commercialization CRADAs</b>                                                                                                        | 2    |

| <i>The Solar America Initiative PV Technology Incubator Program</i>                                                                                | 3    |

| <b>The Leading Edge of Silicon Casting Technology and BP Solar's Mono</b> <sup>2</sup> <b>Wafers</b>                                               | 7    |

| Time Dependent and/or 3D Investigation of Carbon, Nitrogen and Dislocation<br>Distributions In a Silicon Crystal During Solidification Process     | 15   |

| Innovative Crystallization of Multi-Crystalline Silicon Ingots Using Compensated<br>Metallurgical Grade Silicon                                    | 21   |

| <b>Dependency of Power Conversion Efficiency on Donor, Acceptor, and Blocking</b><br><b>Layer Thickness for Small-molecular Organic Solar Cell</b> | 25   |

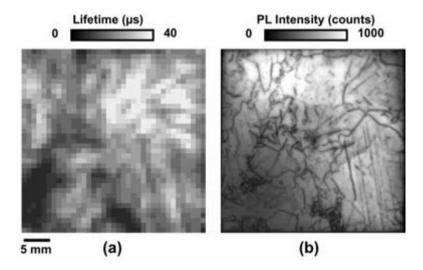

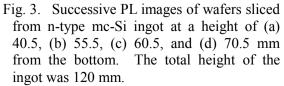

| Crystalline Silicon – Using Experience and Scale to Accelerate Cost Reduction<br>Ahead of Thin-Film PV                                             | 29   |

| <b>SiGen's Kerf-free Wafering Equipment</b>                                                                                                        | 30   |

| Surface Preparation Chemistry for Solar Cell Manufacturing                                                                                         | 31   |

| Alagu Thenappan                                                                                                                                    | 32   |

| Three-Dimensional Analysis of Defects and Quantitative Analysis of Impurities In<br>Multicrystalline Silicon by Photoluminescence                  | 33   |

| <b>Correlation of Defects With Cell Performance Using PVSCAN</b>                                                                                                      | 40  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| <i>Iron In Si: The Visible, the Hidden, and the (Partially) Passivated</i>                                                                                            | 46  |

| <b>PV Silicon Cell Warpage Measurement and Analysis</b>                                                                                                               | 47  |

| Analytical Techniques for PV Si Feedstock Evaluation                                                                                                                  | 48  |

| Effect of Metal Impurities In Silicon Feedstock on Multicrystalline Silicon                                                                                           | 60  |

| <b>Solar Cells</b>                                                                                                                                                    |     |

| <i>Toward a 21% Commercial Silicon Module</i>                                                                                                                         | 68  |

| Progress Towards High Efficiency All-Back-Contact Heterojunction                                                                                                      | 70  |

| <i>c-Si Solar Cells</i>                                                                                                                                               |     |

| Challenges With Testing High-efficiency Si Solar Cells and Modules                                                                                                    | 78  |

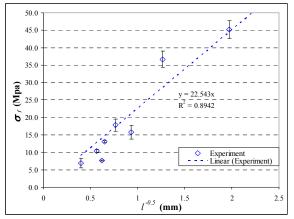

| Mechanical Properties of Multi-Crystalline Silicon: Correlation With<br>Impurities and Structural Defects                                                             | 83  |

| Lifetime and Diffusion Length Mapping and Imaging Techniques for Silicon<br>Solar Cells                                                                               | 84  |

| <b>Photoluminescence Characterization of Silicon Wafers and Silicon Solar Cells</b> T. Trupke, R. A. Bardos, and J. Nyhus                                             | 88  |

| <b>Advances In Si Solar Cell Metallization</b>                                                                                                                        | 96  |

| Minority Carrier Dynamics In Polycrystalline Silicon Solar Cells Investigated By<br>Photo-assisted Kelvin Probe Force Microscopy                                      | 97  |

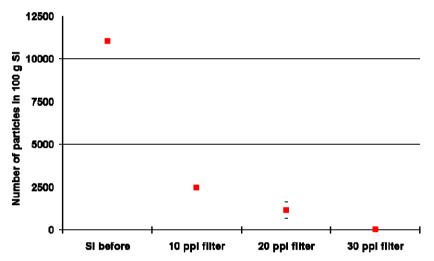

| <b>Recycling of Solar Cell Silicon Scrap By Filtration</b>                                                                                                            | 101 |

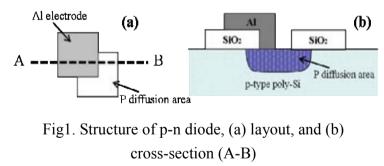

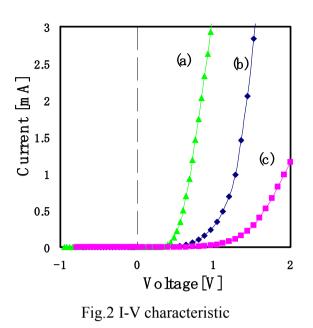

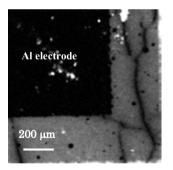

| <i>Evaluation of Multi-crystalline Silicon Substrates With p-n Diode Array</i>                                                                                        | 105 |

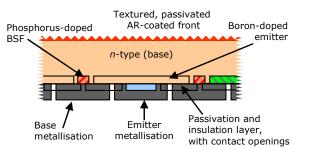

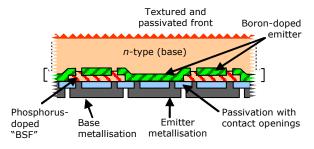

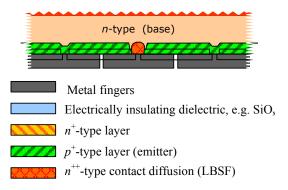

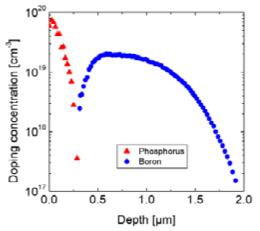

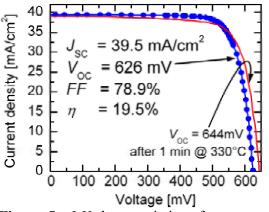

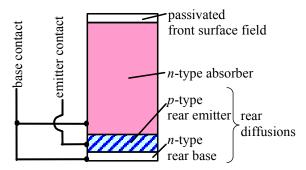

| Passivation of Boron-doped Emitters In Back-junction Buried Emitter Solar CellsBy a Phosphorus-doped Surface LayerNils-Peter Harder, Verena Mertens, and Rolf Brendel | 109 |

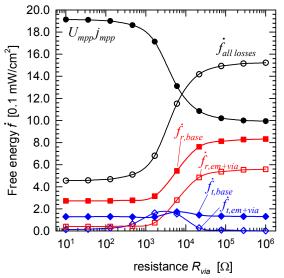

| <b>Free Energy Losses Analysis for Solar Cells</b>                                                                                                                    | 113 |

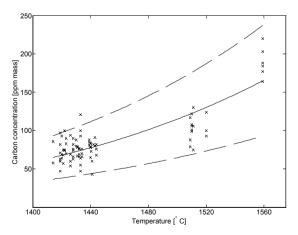

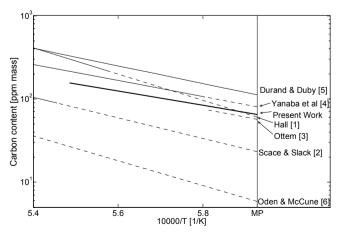

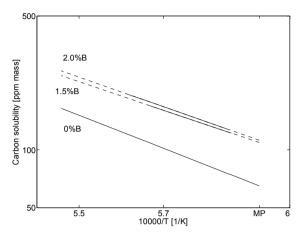

| The Solubility of Carbon In Liquid Silicon Equilibrated With Silicon Carbide andIts Dependence on Boron LevelsH. Dalaker and M. Tangstad                              | 117 |

| <i>Effects of Annealing on Electrical Properties of Polycrystalline Silicon</i>                                                            | 121 |

|--------------------------------------------------------------------------------------------------------------------------------------------|-----|

| <b>Extraction of Principle Stresses from Polariscopy Measurements</b>                                                                      | 125 |

| Qualification of Wafers and Solar Cells Produced From Research-scale<br>Minicaster                                                         | 129 |

| Lock-in Thermographic Shunt Detection and Analysis of Upgraded Metallurgical<br>Grade Silicon Solar Cells                                  | 134 |

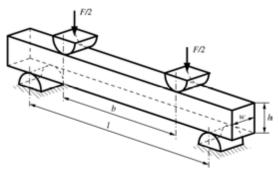

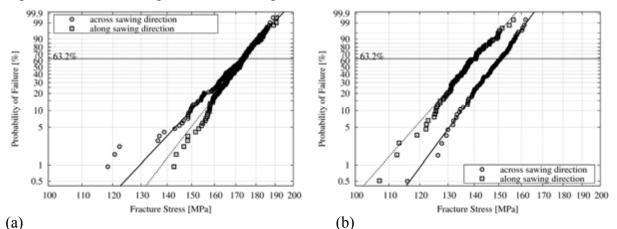

| Understanding the Mechanical Behavior of Multi-crystalline Si Through Characterization of (110) /(100) DSB-HOT Wafers                      | 138 |

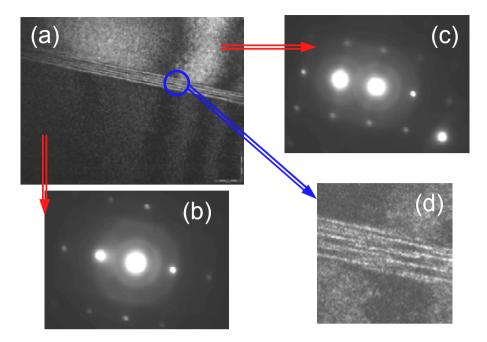

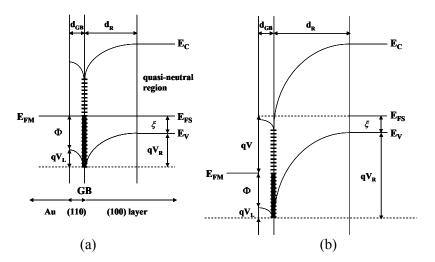

| Electrical Properties of a Metal Contaminated (110) /(100) Si Grain Boundary Prepared By<br>Direct Silicon Bonding                         | 143 |

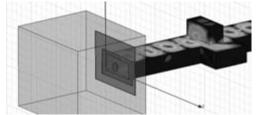

| <b>Analysis of Stresses and Wafer Breakage During Handiling and Transport</b> Xavier F. Brun and Shreyes N. Melkote                        | 147 |

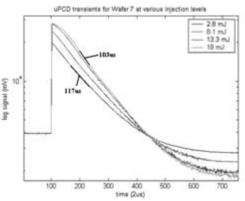

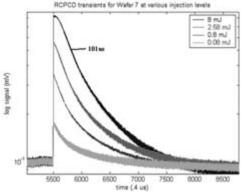

| A Comparison of Transient and Imaging Techniques for Measuring<br>Minority-Carrier Lifetime                                                | 151 |

| <b>Defect Incorporation and Impurity Precipitation In Mono</b> <sup>2</sup> ™ <b>Silicon</b>                                               | 155 |

| Impurity Significance and Sources In Multicrystalline Cast Silicon                                                                         | 159 |

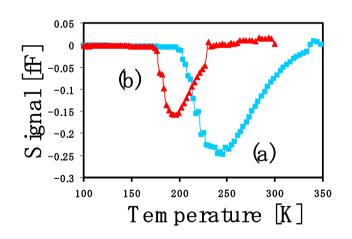

| Hydrogen Passivation of a (110 )/(100) Silicon Grain Boundary Investigated<br>By J-V, C-V, and Capacitance Transient Characterizations     | 163 |

| Intragrain Defects In Polycrystalline Silicon Thin-Film Solar Cells on Glass<br>by Aluminum-Induced Crystallization and Subsequent Epitaxy | 167 |

| Development of Low Cost Plated Contact Solar Cells On High Sheet<br>Resistance Emitters                                                    | 175 |

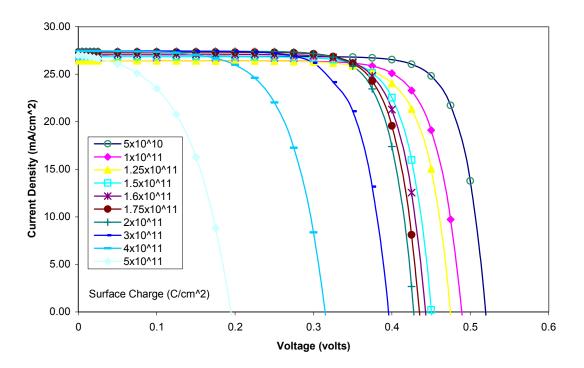

| <b>A Note On Edge Passivation Mechanisms of N/P Mesa Diodes Through Modeling</b> Jesse Appel, Bhushan Sopori, and N. Ravindra              | 180 |

| Mechanical Strength of Mono- and Multicrystalline Silicon Wafers                                                                           | 187 |

| Challenges and Potential Solutions at Making High-Performance Cells From<br>Low-grade Si Feedstock                                         | 191 |

| A Technique for Rapid Cross-Sectioning of Si Solar Cells With Highly<br>Planar, Damage-Free, Edge                                          | 192 |

| Mechanism of Hillock Formation During Chemical Mechanical Polishing       1         Of Multi-crystalline Silicon Wafers       1         Shushan Sopori, Peter Rupnowski, Vishal Mehta, and Monique Ewan |     |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|--|--|

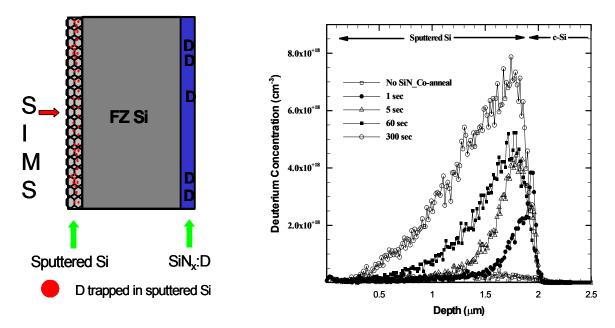

| <i>Migration of Hydrogen in Silicon From PECVD SiN<sub>x</sub> Films</i>                                                                                                                                | 194 |  |  |  |  |

# Workshop Theme: New Directions for Rapidly Growing Silicon Technologies

Bhushan Sopori National Renewable Energy Laboratory 1617 Cole Blvd. Golden, CO 80401

A rapidly growing demand for photovoltaic (PV) energy during last few years has led to a very fast expansion of existing production facilities and a great deal of investment into new start-up companies. PV manufacturers have increased production to reach full capacities, and many new manufacturing facilities have been established whose production has either already started or will do so in the near future. The increased demand, in conjunction with high costs of conventional energy, has fostered a copious flow of venture capital funds into new silicon technologies.

In many cases, these technologies are founded on concepts from cross-cutting fields such as microelectronics, the display industry, and equipment manufacturing. These technologies address new device structures capable of higher commercial cell efficiencies, novel light-trapping structures, use of low-concentration designs, new thin-film silicon structures, and a host of ideas that have been dormant for lack of funds.

A major advancement in the PV industry will come from equipment manufacturers as they address larger cell/module areas, standardized machines, and larger sales in terms of number of machines. New companies bring novel technologies into wafer-based solar cells and also provide a strong impetus to thin-film Si solar cell technologies.

This sharp increase in the Si-PV industry and concomitant emergence of a host of new technologies will bring a multitude of new challenges. Currently, this growth seems to be limited only by the availability of the silicon. While the feedstock issue appears to be at a brink of resolution, there will be new fallouts ranging from a lack of experienced technical population to shortage of other materials needed for wafers, cells, modules, and PV systems.

The theme of this year's workshop reflects potential future changes in the PV industry, expected to arise from synergism of a very rapid growth in PV energy production and a large infusion of investments into many new technologies. These issues will be discussed in a combination of oral presentations by invited speakers, poster sessions, and discussion sessions. Special sessions will be devoted to:

- Feedstock Issues: Monitoring and Qualifying Poly Feedstock

- Progress in Thin-Film Silicon

- Advanced Crystal Growth

- Impurities and Defects in Si: Influence on Solar Cell Performance

In addition, a rump session—"R&D Strategies for a High-Growth Industry (Under Heavy Investment)"—will be held on Sunday evening, August 3.

I hope you enjoy this workshop.

#### Stimulating Commercialization CRADAs

John P. Benner Manager PV Industry Partnerships National Center for Photovoltaics National Renewable Energy Laboratory

The CRADA (Cooperative Research and Development Agreement) is one of several legal documents used for industry to fund research at NREL. The "C" in CRADA is most important as its intent is to permit NREL and a company to work in partnership to move technology to the market faster. The CRADA is unique in providing clear and extensive coverage of ownership and protection for intellectual property (IP), providing simple mechanisms for protecting confidential information and providing clear descriptions of the work each partner will perform. As DOE was developing the Technology Pathway Partnerships (TPP) Announcement they looked carefully at the National Laboratories' interactions with industry and concluded that collaborations fall in two distinct categories – support and partnership – distinguished primarily by the extent of intellectual property involved. The TPPs also established a precedent that DOE was willing to cost-share NREL's contribution to partnerships. In 2008, the PV Program created a new project to fund work at NREL needed to stimulate and expand partnerships with industry. The scope ranges from completion of experiments needed to protect our IP before discussing the technology with potential partners through cost-sharing an expansion to ongoing collaborations. This talk will describe the various agreements for working with NREL, management values related to NREL IP, and this new program to make our industry partnerships even more fruitful.

#### THE SOLAR AMERICA INITIATIVE PV TECHNOLOGY INCUBATOR PROGRAM

Brian Keyes, Martha Symko-Davies, Rick Mitchell, Harin Ullal, Bolko von Roedern, Lori Greene,

and Scott Stephens<sup>1</sup>

National Renewable Energy Laboratory 1617 Cole Blvd., Golden, CO 80401 <sup>1</sup> U.S Department of Energy

#### INTRODUCTION

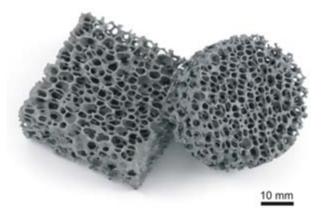

The Solar America Initiative (SAI) PV Technology Incubator Program, funded by the U.S. Department of Energy (DOE) through the National Renewable Energy Laboratory (NREL), has the objective of shortening the timeline for companies to transition prototype and precommercial PV modules into pilot and full-scale manufacture. Entrance opportunities for the incubator project are anticipated every 9-12 months as funding becomes available. This program targets U.S. small businesses with a minimum entrance criterion of a demonstrated PV cell process, lab device, or The successful exit criterion is module. anticipated to be prototype modules and pilot production demonstration of approximately 3 MW/year.

Ten US small businesses received subcontracts from NREL in the fall of calendar year 2007, averaging approximately \$3.0 million each of NREL/DOE funding over an 18-month period. The subcontracts were awarded in two 9-month phases, with the second phase of funding contingent upon successful completion of the first phase deliverables and a Stage-Gate review. The award winners represent a diverse range of technologies including: polycrystalline thin films; thin- and wafer-silicon devices; highefficiency III-V devices; thin-film organics; and concentrating systems.

#### SAI PV INCUBATOR OVERVIEW

The SAI is an integral part of the President's Advanced Energy Initiative (AEI). The AEI is designed to reduce the nation's dependence on foreign sources of energy by promoting broader research and development (R&D) to achieve substantive breakthroughs in a variety energy resources, including of solar photovoltaic (PV) systems. The SAL. authorized under the Energy Policy Act of 2005, represents a significant enhancement of DOE's business strategy of partnering with U.S. industry to accelerate commercialization of PV system R&D to meet cost and installed capacity goals. These SAI goals are to 1) substantively accelerate development of U.S.produced PV systems so that PV-produced electricity reaches parity with the cost of electricity in select grid-tied target markets across the nation and 2) expand the U.S.installed domestic capacity of PV systems to 5–10 gigawatts (GW). The Solar Energy Technology Program's (SETP's) Posture Plan (www.eere.energy.gov/solar/solar america/pu blications.html) illustrates how the SETP aligns with the SAI mission and the President's Advanced Energy Initiative.

To accomplish the goals of the SAI, a multitiered, multi-phased program was established that addresses the near-, mid-, and long-term technological and scientific advances for improved performance, lower cost, and improved reliability of PV system components and installed systems.

The SAI PV Technology Incubator Program is designed to accelerate technologies/processes that have successfully demonstrated a proofof-concept/process in a lab, but are not yet mature enough for large-scale commercial production. The emphasis is currently on the barriers to entering commercialization by 2010. Prototypes of these PV systems and components will be produced on a pilot scale in a relevant operational environment with demonstrated cost, reliability, their or advantages. PV performance and concentrating PV modules are targeted in this phase of the technology development pipeline with goals that include more efficient use of materials. better performance, higher reliability, and improved manufacturing. current solicitation Details on the requirements can be found at www.eere.energy.gov/solar/solar america/pv incubator.html

Responses to past solicitations indicated a need for a "pre-incubator" solicitation. This would include small businesses that had a concept/patent and would proceed to establishing a prototype that would eventually be manufacturable. It is anticipated that this solicitation will be released late this year.

# **EXISTING SUBCONTRACTS**

Ten U.S. companies were awarded subcontracts through a competitive merit review-based process. Analysis of project metrics was conducted for all technology areas. The resulting projects include a diverse set of technological approaches: Inexpensive

Thin-Film and Si: Low and High Concentration: Innovative Thin-Film Manufacturing; and Low-Cost Multi-Junction Cell Production. The \$27M in DOE funds awarded to these ten subcontracts represents 29% of the \$93M worth of R&D taking place under the PV Incubator Program. The current projects subcontracted and recent accomplishments are described below.

# AVA Solar

AVA Solar has demonstrated fully automated, continuous in-line fabrication of CdS/CdTe PV. This project will enable the demonstration extremely low manufacturing of and equipment costs. improved module efficiencies. and the ability for rapid manufacturing capacity expansion.

To date, NREL has verified average efficiency of over 11.0% for small-area thin-film CdTe solar cells. The subcontractor has also demonstrated uniformity of  $\pm/-10\%$  on 16.5" x 16.5" substrates. All processing steps for the fabrication of modules of 16.5" x 16.5' are now installed in the pilot line.

# Blue Square Energy

Manufacture of thin crystalline silicon solar cells by growing a high-purity silicon layer onto a low-cost metallurgical-grade silicon substrate. This approach can produce the high performance and reliability of traditional solar cells with reduced material use and manufacturing costs.

Accomplishments to date include frontsurface passivation, resulting in a surface recombination velocity of <100 cm/s; lighttrapping increases in  $J_{sc}$ ; and efficiencies >14% on 4-cm<sup>2</sup> Cz-Si substrates and >11% on 100-cm<sup>2</sup> Cz-Si substrates.

# CaliSolar

Production of cost-effective solar cells from low-cost and abundant, but impurity-laden, Si feedstock materials. The focus will be on a novel and adapted metallization method that is suitable specifically for using metallurgical Si to manufacture solar cells with over 17% efficiency using multicrystalline Si—and within the next 18 months.

Recently, NREL verified 15%-efficient cells with an optimized front- and rear-contact grid structure.

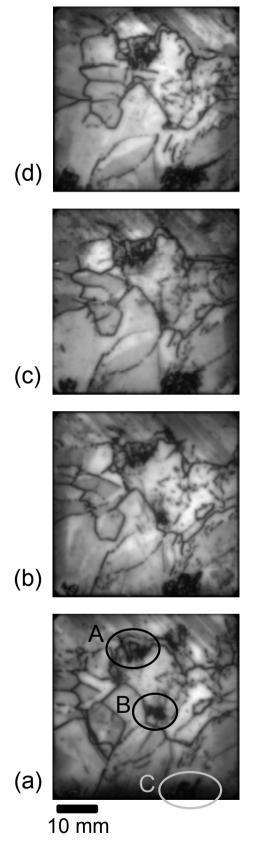

# EnFocus Engineering

A lightweight, low-profile, high-concentration PV module that is fully encapsulated and protected from wind, hail, dust, and moisture. This module will use high-efficiency multijunction cells to generate higher power outputs in area-constrained applications such as rooftops.

Accomplishments to date include improving initial module subassembly efficiency to >23%; developing and implementing design improvements that have increased mechanical durability; implementing damp-heat and mechanical stress testing; designing and building an improved Fresnel optic with >75% transmission efficiency; and demonstrating long-term tracking accuracy of less than 1°.

# MicroLink Devices

MicroLink Devices will develop a low-cost, high-efficiency, dual-junction GaAs-based solar cell for use in 500x concentrator systems. The developed solar cell minimizes GaAs material usage while improving heat dissipation with a potential to reduce cost by 50%.

To date, MicroLink Devices has demonstrated an average cell efficiency of 22% under 1-sun illumination for multiple dual-junction devices. These  $1 - cm^2$  devices were processed on a 4-inch wafer using the epitaxial liftoff fabrication method; this was also demonstrated on a 6-inch wafer.

# **Plextronics**

Commercialization of thin-film organic photovoltaic (OPV) technology. Plextronics will develop higher-efficiency cells while increasing module-lifetime design to enable this ultra-low cost material to compete with traditional PV technology.

Plextronics has confirmed a cell efficiency of 5.4% measured at NREL. This is the highest efficiency ever confirmed for an OPV cell at NREL. Plextronics delivered to NREL a submodule (108-cm<sup>2</sup> active area) that had an efficiency >1.5% after 2000 hours of illumination.

# PrimeStar Solar

Development of commercial CdTe module production based on the NREL 16.5% world record CdTe laboratory solar cell technology. The increased module energy conversion efficiency will lower installation costs and open new markets for CdTe-based thin-film modules.

To date, NREL has verified small-area thinfilm CdTe solar cells with efficiencies >12.0%. For 6" x 6" minimodules, NREL has verified a conversion efficiency >10.0%.

# Solaria

Solaria's PV-multiplying process yields two to three highly efficient cells from one, via solar cell singulation and optical amplification. Solaria's project aims to produce a nontracking, standard module form factor with 2x-3x concentration manufactured in a reliable, high-volume, automated process.

Recently, Solaria representatives stated that they have a purchase agreement with Q-Cells

for 1 GW of cells, and that they have contracted sales for 500 MW of 2x concentrator "supercells."

#### SolFocus

Project involves 500x concentrating PV module emphasizing high reliability and high efficiency to enable large-scale commercial and utility market penetration. A folded reflective design allows for a high optical efficiency and acceptance angle in a compact frame.

Accomplishments to date include developing and constructing a higher-efficiency optic design; optimizing reflectivity and durability of optic coatings for the primary and secondary mirrors; implementing and stresstesting a new module sealant; developing and implementing cell, receiver, and panel performance test methodologies and equipment; and developing a dFMEA (design failure mode effects analysis) process to identify and prioritize initial performance and reliability risks.

#### **SoloPower**

Development of an electroplating-based, highefficiency, low-cost CIGS cell and module manufacturing technology. Advantages of this deposition technique include lower equipment costs, reduced processing times, and increased material utilization.

Recently the company achieved a  $1-m^2$  module that yielded 8.9% efficiency as measured by NREL.

#### CURRENT AND FUTURE SOLICITATIONS

The current PV Incubator subcontracts are undergoing a Stage-Gate review process during the summer of 2008. At this time, an evaluation of progress will occur and a determination to continue with the second 9-month phase of the subcontract will be made. In addition, announcement of the second round of incubator awards stemming from the spring 2008 solicitation are anticipated in August 2008.

Finally, as mentioned above, future entrance opportunities for the incubator project are anticipated every 9–12 months as funding opportunities become available. This would put the next solicitation in early 2009.

#### ACKNOWLEDGEMENTS

This work was supported by the U.S. Department of Energy under Contract No. DE-AC36-99GO10337 with the National Renewable Energy Laboratory.

# The Leading Edge of Silicon Casting Technology and BP Solar's Mono<sup>2</sup> Wafers

Nathan Stoddard<sup>1,a</sup>, Bei Wu<sup>1</sup>, Lisa Maisano<sup>1</sup>, Richard Russell<sup>2</sup>, Joe Creager<sup>1</sup>, Roger Clark<sup>1</sup> and Juan Manuel Fernandez<sup>2</sup>

<sup>1</sup> Technology Department, BP Solar, 630 Solarex Court, Frederick, MD 21703, USA

<sup>2</sup> Technology Department, BP Solar España, Polígono Industrial Tres Cantos, s/n. Zona Oeste, 28760 Madrid, Spain

<sup>a</sup> Nathan.stoddard@bp.com

**Abstract.** A novel crystal growth method has been developed for the production of ingots, bricks and wafers for solar cells. Monocrystallinity is attainable over large volumes with minimal dislocation incorporation. With a novel defect profile of impurities and structural defects, asgrown wafers have averaged 40-80 microseconds in minority carrier lifetime with significantly less lifetime variability than multicrystalline cast wafers. Solar cells of 156 cm<sup>2</sup> size have been produced ranging up to 17.2% in efficiency using a variety of production-ready cell processes. Simulations indicate potential for over 22% efficiency for a back contact cell.

#### Introduction

Cast silicon has been used in the manufacture of solar cells for over 30 years. As alternatives to single crystal silicon grown by Czochralski (CZ) or Float Zone (FZ) methods, lower quality cast and ribbon silicon substrates have disadvantages compared with the considerable perfection achieved in standard single crystal silicon manufacturing. Solar cells made from multicrystalline silicon (multi Si) wafers have historically been limited in electrical efficiency by grain boundaries to some extent but, more significantly, by the high density of dislocations in many grains<sup>1</sup>, and the metallic impurities that aggregate at these structural defects<sup>2</sup>. Many dislocations are generated during growth from high stress points in grain boundaries.<sup>3</sup> Additionally, the difficulty in texturing the multi Si wafer surface has been an optical disadvantage. Nevertheless, multi Si has steadily grown in market share due to higher throughput in kg/hr, simpler manufacturing and resulting lower cost inherent in its growth. Today, multi Si wafers have the largest market share of any technology in the solar industry. The development of multi Si solar cell processing, primarily limited to screen printing, has resulted in efficiency improvements with elements such as silicon nitride passivation, aluminium back surface field and thinner front print line widths. The substrate itself has not changed dramatically since the inception of casting. While ingot sizes have increased 3x in horizontal dimensions and somewhat vertically, the average crystallinity has been little affected. Furthermore, the best lab results of cell efficiency on p-type multi Si have had to rely on relatively long time phosphorus gettering in

order to deal with defect clusters: pockets of transition metals or oxygen precipitates aggregating at tangled dislocations<sup>4</sup>.

It has long been recognized that a cast single crystal product would have inherent advantages over both CZ and multi Si. Early attempts to cast single crystal silicon using the 'heat exchanger method' encountered problems due to multicrystalline nucleation on the floor of the crucible<sup>5</sup>. Despite maximizing the curvature in the crystal growth interface, only bricks with significant multicrystalline volumes could be produced. Conversely, cold crucible casting techniques have been unable to avoid the in-growth of randomly nucleated crystals from the cold walls to the center of the ingot, and generally suffer from even smaller grain sizes than traditional casting.<sup>6</sup>

Recent work at BP Solar has resulted in a new technique for casting ingots with the potential for producing silicon with extremely low defect densities: Mono<sup>2</sup> silicon<sup>7</sup>. The technique involves a proprietary growth nucleation process for the casting of ingots and is used to produce single crystal bricks and wafers, or wafers with specifically chosen grain boundaries. First, the state of the art for industrial casting will be reviewed and then recent production and research results for Mono<sup>2</sup> will be discussed.

#### **State of the Industry**

Recent developments in casting have focused on a few key aspects: grain boundaries, ingot size and doping. Usami *et al.* conducted a number of studies aimed at achieving electrically inactive grain boundaries in p-type silicon.<sup>8,9</sup> In a clever experiment, they were able to watch the nucleation of dendritic crystals from the corner of a crucible, and they contend that the columnar crystals formed by evolution of the dendritic crystals have lower grain boundary energy than the average random grain boundary.<sup>10</sup> In production ingots produced with standard recipes, it is typical to see a dendritic network at the bottom of an ingot, so we may already be benefiting to some extent from this phenomenon. In a cross-over subject, Deutsche Solar has reported low grain boundary activity in ingots cast with n-type material.<sup>11</sup> To date, n-type multi has not been commercialized due to the lack of a production-ready cell process for the substrate. Deutsche Solar has also reported casting of both taller and larger cross-section ingots at increased growth rates indicating good scalability to the casting process.<sup>12</sup>

There has also been a major effort to commercialize electromagnetically cast silicon. Up to 2 ton ingots have been cast using the 'bottomless cold crucible' technique where a copper inductor is used to support a domed mass of liquid by electromagnetic (EM) repulsion. Silicon is metered into the dome from the top while the ingot is solidified and extracted through the bottom. The silicon produced from such a process suffers in a couple ways. Attempts to produce large or seeded crystals have been foiled by the high curvature of the growth interface due to the 1400°C thermal gradient between the water cooled copper and the liquid silicon, which leads to random nucleation of very small crystals at the sides of the ingot. While the central crystals are somewhat higher in quality and can be several millimeters in diameter, there is generally a pronounced low lifetime band protruding in from every side of the ingot and associated with very small crystals and very high dislocation densities.<sup>13</sup> Other issues include the high energy consumption involved in melting in a cold crucible, as well as potential copper contamination and light-induced degradation of solar modules made with EM cast cells.

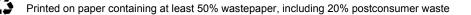

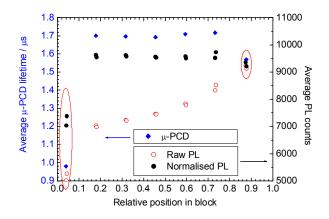

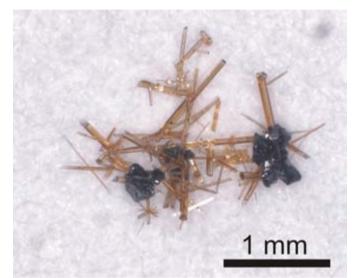

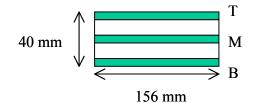

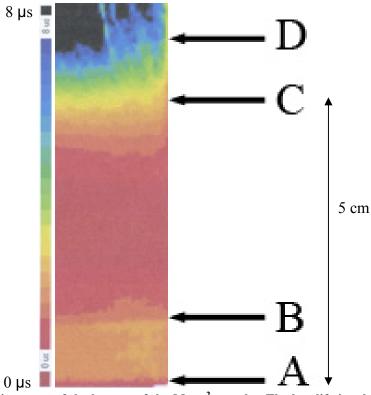

The final issue undergoing heavy experimentation is the incorporation of solar grade, electrically compensated silicon into cast material. In general, this material is around "6N's" pure, or 99.9999% pure, with the primary impurities being carbon, boron, phosphorus and iron. According to the literature, starting with roughly matched levels of boron and phosphorus produces a mostly p-type ingot due to the differing distribution behaviors between the liquid and solid phases.<sup>14</sup> Boron, which incorporates readily at the solidification interface, is prevalent at fairly steady levels throughout the ingot while phosphorus preferably remains in the liquid. As a result, the ingot will be nominally p-type through 80-90% of the ingot, and n-type at the top, see Fig. 1. A number of new suppliers offer solar grade silicon of varying impurity profiles. In general, silicon feedstock with higher phosphorus leads to higher levels of boron being needed, which produces ingots of lower average resistivity and potentially lower lifetime. In the shortage of high purity polysilicon, some silicon manufacturers have chosen to go to an extreme in this tradeoff, producing highly doped wafers that can only produce 11-13% efficiency using screen print cell processing. Another issue with solar grade silicon is carbon content. While cast ingots are typically saturated with carbon and nitrogen from *in situ* contamination, liquid-grown precipitates generally form most heavily at the end of the growth cycle. When using solar grade feedstock that contains silicon carbide particles initially, the chances are higher for incorporating yield-reducing inclusions into the final ingot.

**Fig. 1:** The resistivity of a brick cast with compensated solar grade silicon varies dramatically along the height (x-axis), with a crossover from p-type to n-type near the top of the brick. Diluting the feedstock with intrinsic silicon can increase the base resistivity, but leaves the crossover point unaffected.

The research interests of BP Solar have overlapped with the larger industry on the topics of ingot size and solar feedstock. However, bulk material improvement efforts have been focused on carbon reduction and realizing and perfecting a cast single crystal ingot.

# Experimental

Ingots have been cast in standard production furnaces at BP Solar to the industry standard size of  $690x690 \text{ mm}^2$  and a mass of 265 kg. The ingots have been cut into a 5x5 grid of 12.5 cm bricks, which have been wafered to a nominal thickness between 160 and 200 microns. Wafers are

generally etched in a sodium hydroxide bath to remove saw damage, optionally textured with a pyramidal etch or isochemical texturing, and can be phosphorus-diffused either in a belt furnace or in a tube furnace. In some cases, groove diffusion is performed by making laser grooves in a silicon nitride mask and using a relatively heavy tube diffusion. For minority carrier lifetime measurements, bricks are measured as-cut without passivation, while wafers are measured with methanol iodine passivation after having any processing stripped back. Mapping has been performed using SemiLab WS2000 microwave photo-conductance decay equipment.

#### **Results and Discussion**

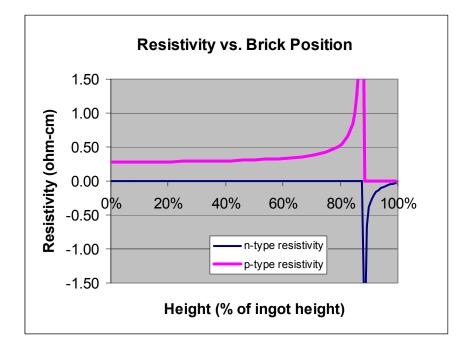

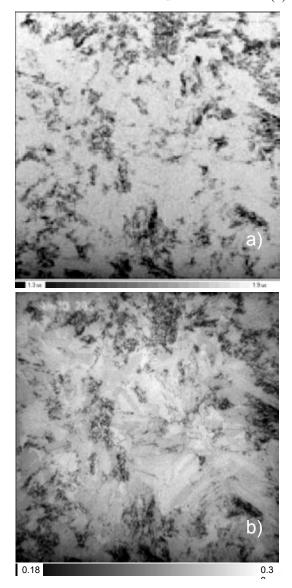

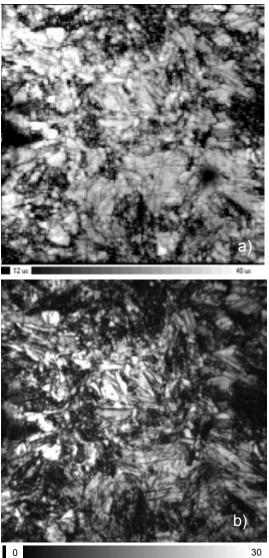

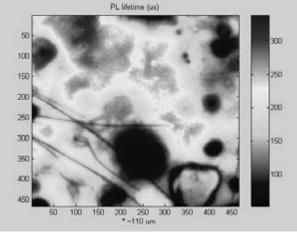

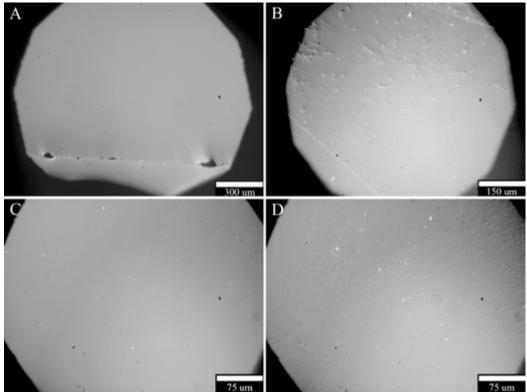

**Bricks and Wafers:** A broad survey of structural defects reveals a considerable difference between traditional multicrystalline cast silicon and Mono<sup>2</sup> silicon. Examples of selectively etched 12.5cm wafers from cast ingots are shown in Fig. 2, where heavily dislocated grains appear as dark regions. Studies of minority carrier lifetime have shown that the dislocation density controls the grain-to-grain lifetime variations in multi Si even on a sub-millimeter scale.<sup>15</sup> Furthermore, the lifetimes in heavily dislocated grains, with dislocation densities > 10<sup>6</sup>

cm<sup>-2</sup>, do not recover to 'good grain' levels as a result of phosphorus diffusion and hydrogen passivation.

**Fig. 2:** Multi Si (left) and Mono<sup>2</sup> (right) wafers after selective etching. Darker areas have higher densities of structural defects, mostly dislocations.

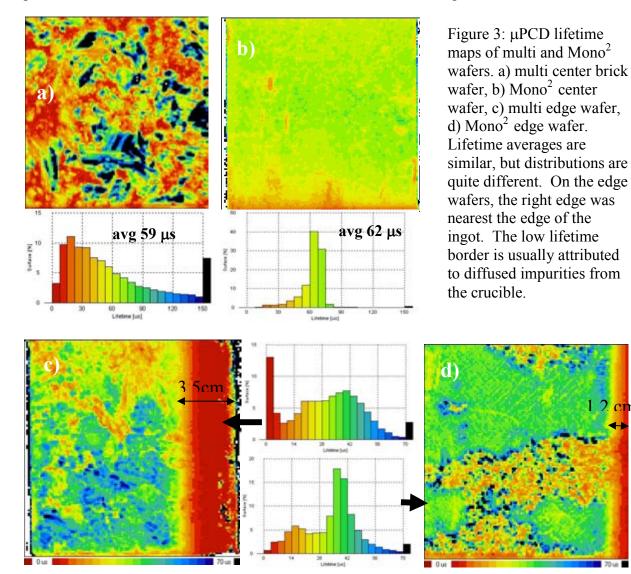

The absence of large angle grain boundaries in  $Mono^2$  is not itself taken to be the chief benefit. In fact, due to the relatively large average grain size, the lifetime of multicrystalline wafers is determined primarily by grain-to-grain variations in dislocation density and not by the electrical activities of the boundaries themselves. In Fig. 3, minority carrier lifetime maps and histograms are shown for as-grown multi and  $Mono^2$  wafers from similar positions in an ingot. While the average lifetimes for the two wafers are similar, the two maps could hardly be more different. The distribution of the multicrystalline wafer is typical for a wafer coming from one of the centrally positioned bricks. While some grains have extremely high lifetimes, the majority of grains fall below 30 microseconds. According to simulations, variations in lifetime cause a decrease in open circuit voltage from the V<sub>oc</sub> that would be predicted for a wafer with a given average lifetime value.<sup>16</sup> According to this work, a ratio of good to bad lifetime in the 20:1 range can pull down Voc on a cell by up to 60 mV relative to a uniform wafer with the same average. By contrast, the lifetime of Mono<sup>2</sup> wafers is more tightly distributed, with a typical lifetime variation closer to the 2:1 range, resulting in minimal loss (<10 mV) from the ideal case.

In examining a series of wafers ranging from the bottom to the top of a brick, as-grown wafer lifetimes start low for a couple centimeters, generally less than 10 microseconds, then through the bulk of the brick remain quite high (40-80 microseconds average), while the top 10% of a brick will see a decrease back down to the 10-20 microsecond range. After a typical phosphorus

diffusion and etch-back, the low-lifetime wafers at the bottom of the brick will recover to normal Mono<sup>2</sup> lifetime values, while those wafers from the top do not significantly improve. Hydrogenation has been shown to further improve bulk lifetime by up to a factor of 3.

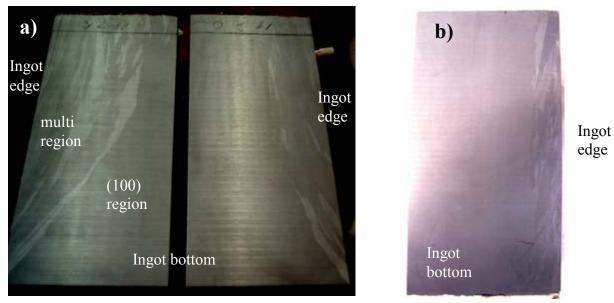

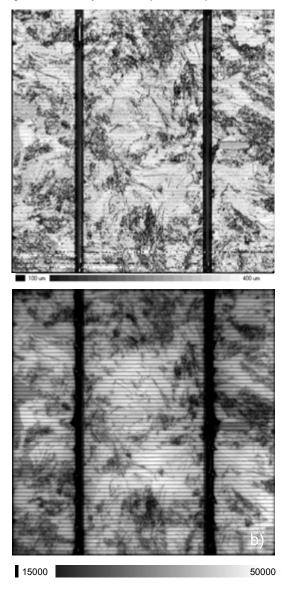

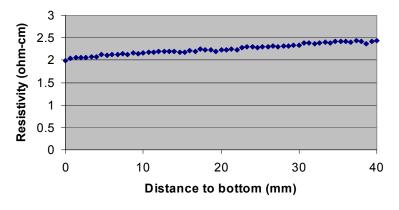

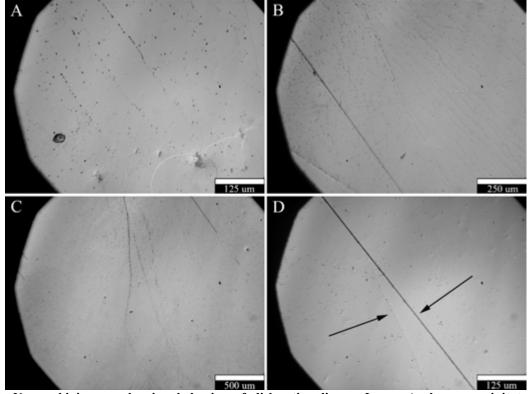

The wafers discussed thus far have been cut from the center of the ingot (e.g. the middle nine bricks of a 25 brick ingot). Next, consider the comparison of wafers cut from the edge of the ingot, see Fig. 4. While the  $Mono^2$  wafer has a lower lifetime region of structural defects, the variability in lifetime is still better than the multi case. The very interesting effect is that the typical low-lifetime region found in wafers cut from edge bricks is almost non-existent on the  $Mono^2$  wafer. Surprisingly, this is the case from the top to the bottom of the brick. This fact presents extra benefit for  $Mono^2$  wafers over multi, and closer competition with CZ.

Having considered wafer quality, now consider the material from a crystalline yield point of view at the brick level. It is not entirely difficult to cast an ingot such that the center bricks end up nominally monocrystalline. Unfortunately, it is considerably more difficult to maintain monocrystallinity throughout the edge bricks. Early tests routinely produced edge bricks that

appeared similar to those in Fig. 4a. With an intention to produce a (100) ingot in order to take advantage of pyramidal texturing, the entire ingot starts as (100) oriented. However, when growing next to randomly nucleated crystals, the (100) orientation competes poorly for surface area, tending to twin along a diagonal at roughly 55° to the bottom. The twinned crystal is generally of poor quality, and can degrade further into more random crystals. Wafers cut from bricks like those in Fig. 4 would appear to have one very large crystal covering 30-90% of the wafer, with the remaining area appearing as typical multicrystalline material. This material has been termed 'Mono/poly' and is typical of sub-optimal seeded casting. After a significant amount of process development and optimization, we have developed techniques to control (100) crystals such that they grow vertically and produce Mono<sup>2</sup> edge bricks. An example of vertical (100) growth is shown in Fig. 4.

**Fig. 4:** Edge bricks showing in-growth of multi (left two), and optimized vertical growth of (100) against the multicrystalline region (right).

# **Cell Results**

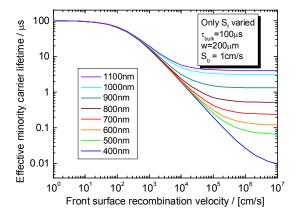

Mono<sup>2</sup> solar cells made at BP Solar have been produced using a variety of surface texturing options in conjunction with standard industrial screen print processing. The (100) wafers can easily be textured with a pyramidal sodium+IPA etch to produce black solar cells. Large batches of wafers have averaged 16.2% electrical efficiency for 12.5cm cells, with some cells ranging as high as 17.0% under AM1.5 illumination. This represents a 1% absolute efficiency gain (6% power gain) over multi wafers made with the same process, and equivalent performance to CZ wafers manufactured with the same process. Wafers made with a sodium hydroxide polish etch and no surface texture have averaged 0.5% higher than multi, while iso-chemically textured wafers have been intermediate between the NaOH etch and the pyramidal performance. Diffusion length has averaged from 500 to 650 microns on screen printed cells as measured using multiple wavelengths on finished cells.

While these results are promising, the real promise of Mono<sup>2</sup> lies in more advanced cell structures. A project has been undertaken to systematically test wafers with various production-

ready advanced techniques. These have been broken down into two categories here: an advanced front with a standard screen print back, and an advanced back with a normal screen print front. The results of the testing on p-type wafers are shown below in Table 1. It is expected that putting the advanced front and back structures together will result in even higher efficiencies. Work is ongoing to produce cells on n-type Mono<sup>2</sup> wafers, with significant promise. Simulations for a novel BP Solar back contact structure on a Mono<sup>2</sup> substrate have estimated in excess of 22% conversion efficiency. On the whole, Mono<sup>2</sup> wafers have had equivalent lifetimes and cell efficiencies to commercially available CZ wafers.

| Process              | Туре      | Voc | lsc | FF   | Average<br>Eff | Number of<br>Cells |

|----------------------|-----------|-----|-----|------|----------------|--------------------|

|                      |           | mV  | А   | %    | %              |                    |

| Screen Print Texture | p-type    | 610 | 5.4 | 76.4 | 16.2           | >2000              |

| Advanced Rear        | p-type    | 635 | 5.4 | 77.6 | 17.2           | 5                  |

| Advanced Front+back  | p-type    | 612 | 5.5 | 77.0 | 17.1           | 4                  |

| Simulated Back       | p-type or |     |     |      |                |                    |

| Contact              | n-type    | 675 | 6.2 | 82.5 | 22.2           | 0                  |

# **Module Results**

In the  $4^{th}$  quarter of 2007, BP Solar produced, sold and installed roughly 200kW of Mono<sup>2</sup> modules in a pilot run. For simplicity's sake, these modules were made using an identical cell process to the standard multi-crystalline product. These modules were installed with power tracking capability, and we now have several months of performance data. On the whole, the Mono<sup>2</sup> modules are averaging 6% more power than their multicrystalline counterparts, even though they have no wafer texturing. Because the wafers come from cast ingots, they have low oxygen concentrations and have lost no more than 0.5% of power to light induced degradation, making their field performance better than traditional mono modules. This year, BP Solar will increase Mono<sup>2</sup> casting capacity to 25% of the total, with plans to significantly increase this proportion in 2009 and 2010.

#### Conclusions

The Mono<sup>2</sup> process has been demonstrated to produce single crystal ingots suitable to make solar cells averaging 17.2% using production-ready processes. As an absolute base case, untextured screen print Mono<sup>2</sup> modules have been shown to produce 6% more power in the field than multi Si modules. Historically, the dynamics of market competition for different technologies in the photovoltaic sector have typically been framed in terms of a trade-off: one can have high energy efficiency or low cost of manufacture. Different players have chosen to operate at different ends of the spectrum, from back-contact 20+% silicon to <10% thin film, but all result in a surprisingly similar installed \$/Watt cost. Mono<sup>2</sup> technology can offer the best of both worlds. Single crystal casting is still in its infancy, and there is reason to believe that significant improvements will be attainable in defect management over what can be manufactured today. But even with demonstrated lifetimes, electrical efficiencies in excess of 22% are attainable. With today's single crystal cast ingot, BP Solar believes that the Mono<sup>2</sup> substrate together with new technology in cell processing will break out of the historical trade-off dynamics and move to a place where low cost together with high electrical efficiency achieve widespread grid parity.

#### Acknowledgements

The authors would like to recognize the US DOE SAI program, as well as several colleagues: Jim Cliber, Doug Stark, Eugene Rhee, Monte Lewis, Irem Nase, Paul Von Dollen and Victor Mohyla.

# References

<sup>1</sup> O. Schultz, S.W. Glunz, S. Riepe and G.P. Willeke: Prog. Photovolt: Res. Appl. Vol. 14 (2006), p. 711

<sup>2</sup> W. Schröter, V. Kveder, M. Seibt, H. Ewe, H. Hedemann, F. Riedel and A. Sattler: Mat. Sci. and Eng. B Vol. 72 (2000), p. 80

<sup>3</sup> K.C. Yoo, S.M Johnson and W.F. Regnault, J. Appl. Phys., Vol. 157 (1985), p. 2258

<sup>4</sup> B.L. Sopori: Mat. Sci. Forum Vol. 258 (1997), p. 527

<sup>5</sup> F. Schmid: J. Electronic Materials Vol. 5 (1976), p. 436

<sup>6</sup> F. Durand: Solar Energy Materials & Solar Cells Vol. 72 (2002), p.125

<sup>7</sup> Mono<sup>2</sup> is a trademark of BP Solar

<sup>8</sup> N. Usami, K. Kutsukake, T. Sugawara, K. Fujwara, W. Pan, Y. Nose, T. Shishido, and K. Nakajima, Jap. J. Appl. Phys. -1 Vol. 45 (2006), p. 1734

<sup>9</sup> N. Usami, K. Fujiwara and K. Nakajima, Japanese Patent Application 2006227131 "METHOD FOR PRODUCING BULK POLYCRYSTALLINE MATERIAL", PUBLICATION NUMBER-08050194 JP

<sup>10</sup> K. Fujiwara, W. Pan, K. Sawada, M. Tokairin, N. Usami, Y. Nose, A. Nomura, T. Shishido, K. Nakajima, J. Crystal Growth Vol. 292 (2), (2006), p. 282

<sup>11</sup> P. Woditsch, G. Stollwerck, C. Hassler, W. Koch, US Patent 6576831 "Multicrystalline silicon having a low proportion of active grain borders"

<sup>12</sup> A. Mueller, M. Ghosh, R. Sonnenschein, P. Woditsch, Mat. Sci. and Eng. B, Vol. 134 (2006) p. 257

p. 257

<sup>13</sup> I. Perichaud, S. Martinuzzi, and F. Durand, SOLAR ENERGY MATERIALS AND SOLAR CELLS, Vol. 72 (2002) p. 101

<sup>14</sup> E. Enebakk *et al*, PCT Patent Application PCT/NO2004/000003 "Silicon Feedstock for Solar Cells"

<sup>15</sup> N. Stoddard, B. Wu, I. Witting, M. Wagener, Y. Park, G. Rozgonyi and R. Clark, Sol. State Phenom. Vol. 131 (2007) p. 1

<sup>16</sup> K. Nakayashiki, V. Meemongkolkiat, A., IEEE Transactions on Electron Devices. Vol. 52 (2005), p. 2243

# Time dependent and/or 3D investigation of carbon, nitrogen and dislocation distributions in a silicon crystal during solidification process

Koichi KAKIMOTO

Research Institute for Applied Mechanics, Kyushu University 6-1, Kasuga-Koen, Kasuga 816-8580, JAPAN e-mail: Kakimoto@riam.kyushu-u.ac.jp

#### ABSTRACT

The unidirectional-solidification process is a key method for large-scale production of multi-crystalline silicon for use in highly efficient solar cells in the photovoltaic industry. Since the efficiency of solar cells depends on the crystal quality of the multi-crystalline silicon, it is necessary to optimize the unidirectional-solidification process to control temperature and impurity distributions in a silicon ingot. We developed a transient global model for the unidirectional-solidification process. We carried out calculations to investigate the temperature and impurity distributions such as carbon and nitrogen, and dislocation density in a silicon ingot during solidification process by taking into account phase diagram. Solid-liquid interface in rectangular crystals is also investigated by using 3D global model.

#### 1. Introduction

The unidirectional-solidification method is a key method to produce multi-crystalline silicon for use in highly efficient solar cells [1]. Since the efficiency of solar cells depends on the quality of the multi-crystalline silicon, which is determined by the crystallization process such as cooling rate and rotation rate of a crucible, it is important to investigate and optimize the unidirectional-solidification process to control the distributions of temperature and impurity in a silicon ingot during the solidification process.

Numerical calculation has become a powerful tool for investigation and optimization of a unidirectional-solidification process and crystal growth process with development of computer technology and new algorithms [2-12]. Since a unidirectional-solidification furnace has a highly nonlinear thermal system, transient simulation with global modeling is an essential tool for investigation and improvement of a unidirectional-solidification process from melting to cooling through the solidification process. We developed a transient code with a global model for the unidirectional-solidification process, and we carried out calculations to investigate distributions of temperature and impurity in a silicon ingot during the unidirectional-solidification process [13, 14].

#### 2. Model Description and Computation Method

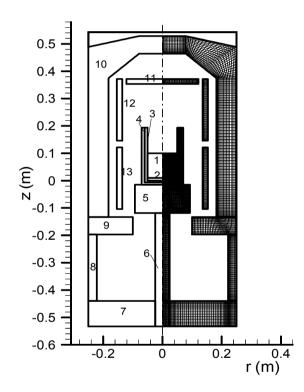

Figure shows the configuration and dimensions of small 1 а unidirectional-solidification furnace for producing multi-crystalline silicon. The melt, a crvstal. a crucible and a pedestal are denoted as 1, 2, 3, 4, 5 and 6, respectively. Thermal shields are labeled as 7 to 11. The two heaters marked by 12 and 13 were set to the furnace. The following points are assumed in the present calculation: (1) the geometry of the furnace configuration is axisymmetric, (2) radiative heat transfer is modeled as diffuse-gray surface radiation, (3) the melt flow in the crucible is laminar and incompressible, and (4) the effect of gas flow in the furnace is neglected.

Fig. 1 Configuration and computation grid of a casting furnace. The melt, a crystal, a crucible and a pedestal are denoted as 1, 2, 3, 4, 5 and 6, respectively. Thermal shields are labeled as 7 to 11. The number of 12 and 13 show multi heater.

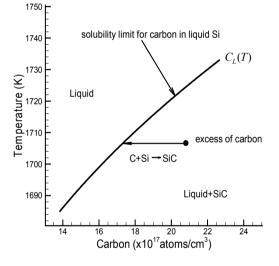

Fig. 2 Schematic of SiC particle precipitation with the Si-C phase diagram in the Si-rich domain.

The domains of all components in a unidirectional-solidification furnace are subdivided into a number of block regions, as shown in the left part of Fig. 1 in order to establish a discrete system for numerical simulation. Each block is then discretized by structured grids, which is shown in the right part of Fig. 1. Conductive heat transfer in all solid components, radiative heat exchange between all diffusive surfaces in the unidirectional-solidification furnace, and the Navier-Stokes equations for the melt flow in the crucible are coupled and solved iteratively by a finite volume method in a transient condition.

Figure 2 shows a schematic of SiC particle precipitation in Si-melt with the Si-C phase diagram in the Si-rich domain [15], in which the solubility limit of carbon in Si-melt  $C_L(T)$  is approximated by a polynomial function:

$$C_L(T) = 8.6250 \times 10^{-4} T^2 - 2.7643T + 2222.9.$$

<sup>(1)</sup>

The units for carbon concentration and temperature in eq. (1) are  $10^{17} atoms/cm^3$  and K, respectively. With solidification of the molten silicon and upward movement of the solidification interface in the crucible during the solidification process, the carbon concentration in the melt increases due to the small segregation coefficient of carbon in silicon. If the carbon concentration exceeds the local solubility limit, excessive carbon precipitates and the following chemical reaction occurs:

$$Si + C \rightarrow SiC$$

(2)

The substitutional carbon is thus reduced and the same amount of SiC particles is generated in the Si-melt. The formation rate of SiC particles and the destruction rate of substitutional carbon are equal and proportional to the super-saturation degree of substitutional carbon and the speed of the chemical reaction (2):

$$G_{SiC} = -G_C = \alpha (C_C - C_L(T)), \quad \text{when } C_C > C_L(T), \quad (3)$$

$$G_{SiC} = -G_C = 0, \quad \text{when } C_C \le C_L(T), \quad (4)$$

where  $G_{SiC}$  and  $G_C$  are the formation rates of SiC particles and substitutional carbon, respectively. Minus values denote the destruction rate. The coefficient  $\alpha$  is a factor correlating the particle formation rate and the chemical reaction rate in (2). For convenience, we name it the reaction rate coefficient. It is assumed that the chemical reaction (2) occurs rapidly when carbon is super-saturated in the melt. The value of  $\alpha$  will be determined in our modeling.

With these assumptions, the governing equations for the concentrations of substitutional carbon and SiC particles in Si-melt can be expressed as follows:

$$\frac{\partial C_c}{\partial t} + \mathbf{V} \cdot \nabla C_c = \nabla \cdot (D_c \nabla C_c) + G_c \quad \text{for substitutional carbon,}$$

(5)

$$\frac{\partial C_{SiC}}{\partial t} + \mathbf{V} \cdot \nabla C_{SiC} = G_{SiC} \qquad \text{for SiC particles.} \tag{6}$$

The initial conditions for both impurities in the melt are defined as follows: $C_c = C_0$ for substitutional carbon,(7) $C_{sic} = 0$ for SiC particles,(8)

where  $C_0$  is the carbon concentration in the silicon feedstock. The zero mass flux condition is applied at crucible walls and the top surface for both impurities. At the melt-solidified ingot interface, the segregation effect is taken into account for substitutional carbon and the continuity condition is applied for SiC particles. The effective segregation coefficient of carbon in silicon was set to 0.07. Nitrogen concentration in the process was also carried out by imposing the segregation coefficient of 0.0007.

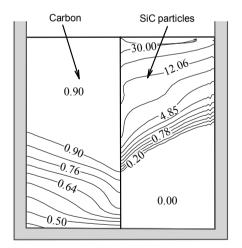

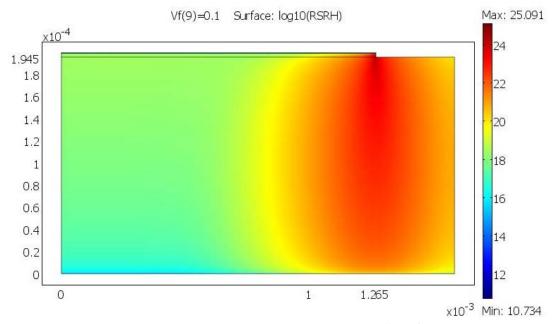

Fig. 3 Distributions of substitutional carbon (left) and SiC particles (right) in a cross-plane of the ingot solidified in a fast-cooling process. Unit of concentration is  $10^{17} atoms / cm^3$ .

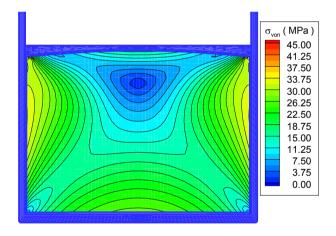

Fig. 4 Von Misess stress distribution for the rigid boundary condition on the ingot and crucible wall interface.

For axisymmetric thermoelastic stress, analysis is performed in the silicon ingot using a displacement-based thermo-elastic stress model, which has been widely used for SiC and AlN crystal growth processes [16–18]. Since the gravity is negligible compared with the thermal stress, it is not considered in the equilibrium equations.

#### **Results and discussion**

Figure 3 shows the distributions of substitutional carbon (left) and SiC particles (right) in a cross-plane of the solidified ingot. It can be seen that particle precipitation begins in the central area when the fraction solidified reaches about 30%. The SiC particles are clustered at the center-top region of the ingot, where the concentration of substitutional carbon is almost constant. This distribution pattern is due to the melt-solidified ingot interface shape, which is concave to the solid side throughout the solidification process.

The impurity level in silicon feedstock has significant impact on the conversion efficiency of a multicrystalline silicon solar cell. We carried out a series of computations for the same fast-cooling solidification process but with different carbon concentrations in silicon feedstock ( $C_0$ ). The obtained concentration distributions of substitutional carbon and SiC particles along the center axis of the solidified ingot are compared in Fig. 4 with the carbon concentration in silicon feedstock ranging from  $1.26 \times 10^{16} atoms/cm^3$  (equivalent to 0.1 ppmw) to  $6.30 \times 10^{17} atoms/cm^3$  (equivalent to 5.0 ppmw). When  $C_0$  is  $1.26 \times 10^{16} atoms/cm^3$ , no SiC particles are precipitated in the ingot and there is only a very thin layer rich in substitutional carbon at the top. When  $C_0$  increases to more than  $1.26 \times 10^{17} atoms/cm^3$ , the content of SiC particles increases significantly in magnitude as well as in space in the solidified ingot. It is thus necessary to control the carbon concentration in silicon feedstock to less than  $1.26 \times 10^{17} atoms/cm^3$ , which is equal to 1.0 ppmw.

Figure 4 shows the von Mises stress distribution in the silicon ingot. The results show that the maximum value of the stress distributes at the periphery of the crystals. In this case, we imposed elastic deformation. When we consider inelastic effects including dislocation distribution, the stress reduced about 15times smaller than that with an assumption of elastic deformation shown in Fig. 4.

#### 4. Summary

A transient global model and code were developed for analyzing a casting process. We predicted the distribution of temperature and iron distributions as a function of time. The results showed that iron diffused even after the end of solidification, which is due to the rather small activation energy of iron in silicon. A U-shaped distribution of iron in the z-direction could be predicted by using the newly developed code, which can calculate transient phenomena of a casting process of silicon for photovoltaic devices.

#### Acknowledgements

This work was supported by a NEDO project, a Grant-in-Aid for Scientific Research (B) 19360012 and a Grant-in-Aid for the creation of innovation through business-academy-public sector cooperation from the Japanese Ministry of Education, Science, Sports and Culture.

#### References

- [1] D. Sati, R. Einhaus, Sol. Energy Mater. Sol. Cells 72 (2002) 27.

- [2] R. Kvande, O. Mjos, B. Ryningen, Mater. Sci. Eng. A 413-414 (2005) 545.

- [3] H. J. Moller, L. Long, M. Werner, D. Yang, Phys. Status Solidi A 171 (1999) 175.

- [4] S. Pizzini, et al., J. Electrochem. Soc. 135 (1988) 155.

- [5] J. Bauer, O. Breitenstein, J. P. Rakotoniaina, Proceedings 21<sup>st</sup> EUPVSEC, Sept. 4-8, 2006, Dresden, Germany, p.1115.

- [6] K. Arafune, E. Ohishi, F. Kusuoka, H. Kawai, H. Sai, Y. Ohshita, M. Yamaguchi, Renewal Energy 2006 Proceedings, 9-13 Oct. 2006, Chiba, Japan, p.407

- [7] A. Muhlbauer, V. Diers, A. Walther, J. Crystal Growth 108 (1991) 41.

- [8] P. S. Ravishankar, J. P. Dismukes, W. R. Wilcox, J. Crystal Growth 71 (1985) 579.

- [9] F. Dupret, et al., Int. J. Heat Mass Transfer 33 (1990) 1849.

- [10] A. T. Kuliev, N. V. Durnev, V. V. Kalaev, J. Crystal Growth 303 (2007) 240.

- [11] J. J. Derby, L. Lun, A. Yeckel, J. Crystal Growth 303 (2007) 114.

- [12] D. Vizman, J. Friedrich, G. Müller, J. Crystal Growth 303 (2007) 231.

- [13] L. J. Liu, K. Kakimoto, Int. J. Heat Mass Transfer 48 (2005) 4481.

- [14] L. J. Liu, S. Nakano, K. Kakimoto, J. Crystal Growth 292 (2006) 515.

- [15] H. Laux, Y. Ladam, K. Tang, E. A. Meese, Proceedings 21<sup>st</sup> EUPVSEC, Sept. 4-8, 2006, Dresden, Germany.

- [16] R. H. Ma, Ph.D. thesis, State University of New York at Stony Brook (2003).

- [17] B. Wu, R. H. Ma, H. Zhang, M. Dudley, R. Schlesser, Z. Sitar, J. Cryst. Growth 253 (2003) 326–339.

- [18] R. G. Lee, A. Idesman, L. Nyakiti, J. Chaudhuri, J. Appl. Phys. 102 (2007) 063525.

# Innovative Crystallization of Multi-Crystalline Silicon Ingots using Compensated Metallurgical Grade Silicon

J. Kraiem<sup>1</sup>, R. Einhaus<sup>1</sup>, S. Dubois<sup>3</sup>, N. Enjalbert<sup>3</sup>, B. Drevet<sup>3</sup>, F. Servant<sup>3</sup>, D. Camel<sup>3</sup>, F. Lissalde<sup>2</sup>

<sup>1</sup> Apollon Solar, 23 rue Claudius Collonge, 69002, Lyon, France

<sup>2</sup> Cyberstar, Parc Sud Galaxy, 1 rue des Tropiques, 38435, Echirolles, France

<sup>3</sup> CEA-INES, 50 avenue du Lac Léman, 73377, Le Bourget du Lac, France Email : kraiem@apollonsolar.com

#### Abstract

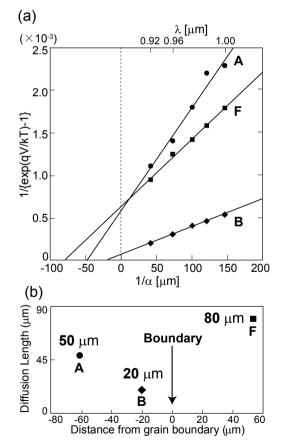

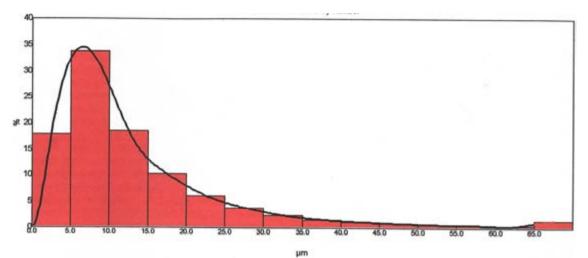

The presented work is a part of the French Photosil project which deals with the plasma purification and crystallization of metallurgical grade silicon. In this paper we present results obtained from a multi crystalline silicon ingot made from 100% purified metallurgical silicon (SoG). Despite a relatively high concentration of remaining impurities in the feedstock after purification, especially boron and phosphorous (2.510<sup>17</sup> and 3.510<sup>17</sup> cm<sup>-3</sup> respectively), solar cells obtained from the crystallized ingot exhibit an average efficiency of 14%. More surprising, analysis of these solar cells shows an increase of the minority carrier diffusion length with the ingot height, i.e with the degree of compensation. Indeed, due to the more efficient segregation of phosphorous during crystallization the upper part of the ingot presents regions of strong compensation and even an inversion of polarity type from p-type to n-type at 70% of its height. However, this reduced material yield is counterbalanced by lowering silicon losses due to ingot cropping. The innovative crystallization process used is based on a new furnace configuration and on a high purity quartz crucible allowing a lower contamination of the ingot during crystallization. This innovative crystallization process is also described.

#### 1. Introduction

As the demand for high-quality solar grade Si feedstock exceeds supply and drives prices upwards, new solar grade silicon production techniques are being developed [1]. Currently, among the different projects to overcome this shortage by establishing a dedicated solar silicon production, two major routes can be distinguished. The first, called the chemical route, is related to the purification of silicon by means of a simplified Siemens process, consisting of decomposing trichlorosilane by CVD [2]. The alternative route, known as the metallurgical route, involves obtaining solar-grade silicon directly from metallurgical silicon [3]. This route for production can be five times more energy efficient than the conventional Siemens process that uses more than 200 kWh/kg [4]. However, metallurgical route production techniques are generally less efficient in removing dopants and an important point related to the use of purified

metallurgical Silicon is the presence of both, n-type and p-type dopant atoms (Phosphorous and Boron).

Moreover, due to their relatively high segregation coefficients with an important difference in their absolute value ( $k_b=0.8$ ,  $k_p=0.35$ ), boron and phosphorous are not easily removable by segregation and have different segregation behavior. As a result, during the crystallization of a multi crystalline Si ingot from such a feedstock, there are 2 major consequences: firstly, similar presence of p-type and n-type dopant atoms changes the free carrier concentration and consequently the resistivity through the ingot height. Secondly, the upper part of the ingot often turns to n type, which drastically reduces the material yield i.e. furnace productivity.

However, the most important question related to this material is the compensation effect. Up to now only few studies have been devoted to the effect of dopant compensation on electrical properties. If on one hand, some studies are suggesting that compensated dopants could have a significant impact on the carrier lifetime [5], others studies are proposing that electrical compensation of boron with donors, like P could be a solution [6]. Based on this variety of results, one can imagine that there is a frontier between beneficial/detrimental effects which is still an unknown, and further investigations are required.

#### 2. Innovative Crystallization Process

Considering the characteristics of the purified metallurgical silicon i.e. a relatively high concentration of residual impurities and a poor material yield of the ingot grown due to the n-type region a crystallization process adapted for that kind of feedstock was developed.

This innovative process is based on two important key features:

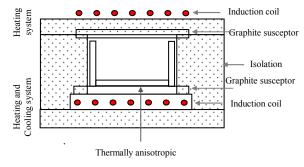

The first one is a new thermal furnace topology consisting of two independently controlled inductive heating elements below and above the crucible in combination with a lateral thermal insulation. This new thermal configuration (fig.1) is well adapted for establishing high temperature gradients (>10K/cm) and a planar solid/liquid interface, which are especially beneficial for the segregation of remaining impurities in lower quality silicon at high solidification velocities.

The second element is a thermally anisotropic quartz crucible. Contrary to the configuration presently employed by the industry whereas the crucible bottom is characterized by an important thermal resistance (due to the low thermal conductivity of fused silica), our crucible presents an optically transparent bottom and opaque side walls. By this way, during crystallization the heat flux is easily extracted through its transparent bottom via IR radiation, whereas the opaque crucible walls support lateral thermal insulation, thus allowing application of a larger thermal gradient so higher crystallization rate. In a second aspect, the use of quartz instead F

**Figure 1:** Schematic view of the principal elements of the new crystallisation furnace

**Figure 2:** Photo of a 200x200x100mm<sup>3</sup> anisotropic quartz crucible with transparent bottom and opaque side walls.

of fused silica as crucible material drastically reduces the contamination of the ingot by solid state diffusion. Indeed, as shown in table 1 the total amount of impurities presents in quartz is much lower than in standard crucible material i.e. fused silica. This allows for improving the material yield by reducing cropping losses, since the ingot regions in contact with the crucible wall get less contaminated during crystallization.

| Element | Standard<br>Crucible | Quartz<br>Crucible |  |  |

|---------|----------------------|--------------------|--|--|

| Mg      | 10                   | 0.8                |  |  |

| Al      | 950                  | 17                 |  |  |

| Ti      | 60                   | 2.5                |  |  |

| Mn      | 2                    | 0.1                |  |  |

| Fe      | 120                  | 0.8                |  |  |

| Ni      | 1                    | 0.1                |  |  |

**Table 1:** Impurity concentrations in standard grade silica crucible [7], and quartz crucible (ppmw).

#### 3. Experimental Results and Discussion

Crystallization experiments were carried out in a lab-scale furnace using the innovative crystallization process. Two ingots with different types of silicon were grown: (i) Electronic grade (EG) silicon, boron doped with a resistivity of  $0.5\Omega$ cm; (ii) Purified metallurgical Silicon (SoG) from PHOTOSIL with remaining impurities concentrations as shown in Table 2. It has to be noted that the purification results reflect an earlier status of the project. In the meantime Boron concentrations of 1 ppmw are regularly obtained.

| Element | Al | В    | Ca  | Cr | Cu | Fe | Ni | Р    | Ti | V  |

|---------|----|------|-----|----|----|----|----|------|----|----|

| Ppmw    | <5 | ~2-3 | 8.8 | 2  | <2 | 26 | <2 | ~6-8 | <1 | <2 |

**Table 2:** Impurity concentrations in Photosil purified metallurgical silicon.

After crystallization, the two resulting 6 kg ingots were cut into wafers including the bottom part of the ingot, which is usually removed on standard ingots, in order to assess the level of contamination from the quartz crucible.

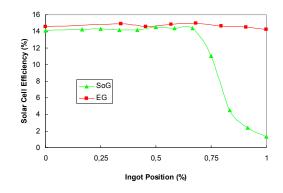

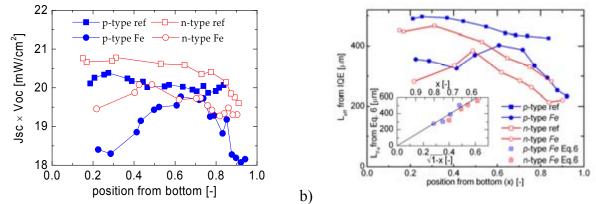

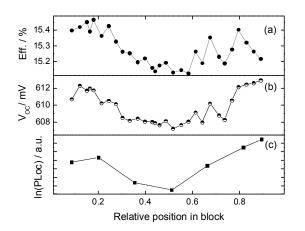

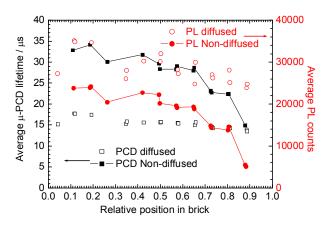

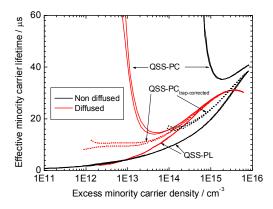

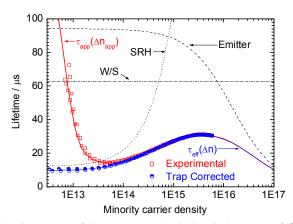

Fig. 3 shows the obtained efficiencies of both ingots as a function of their height. In case of the EG ingot the efficiency distribution is very uniform at a high level of 15% from the bottom to the top of the ingot. In case of the ingot from PHOTOSIL Silicon, numerous observations can be made: (i) As expected, due to the high residual concentration of phosphorous and its more efficient segregation compared to boron, the ingot turns n-

**Figure 3:** Solar cell efficiencies as a function of ingot position for ingots from EG Silicon and PHOTOSIL silicon.

type at around 70% of its height, from which point the solar cells efficiencies drastically drop. (ii) As with EG ingot, no significant degradation of the efficiency for solar cells from the bottom part of the ingot was observed, which confirms the interest of quartz as crucible material. Moreover, the same result can be expected from the periphery of the ingot, so a higher material yield can be

reached for ingots grown using this technique, limiting the loss due to n-type inversion; (iii) Relatively high solar cell efficiencies were obtained (14%) in the p-type region in regards to the residual impurities concentration of the feedstock, especially boron and phosphorous concentrations. More surprisingly, but not perceptible on the graph, is the fact that best solar cells (14.3%) were obtained just before the change of polarity type i.e. in the strongest compensated region.

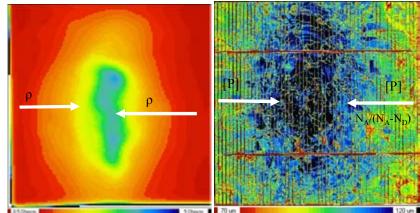

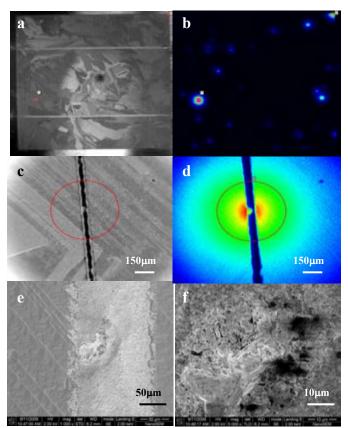

Figure 4: Resistivity (left) and Ln (right) mappings of a compensated SoG multicrystalline silicon cell.

Characterizations of wafers and solar cells were then conducted. LBIC and resistivity mappings show a perfect match between the minority carrier diffusion length Ln and resistivity (fig.4). Indeed, the higher Ln value (120µm) is located in the wafer center i.e. in the highest resistive region while the lower Ln value (75µm) is situated in the wafer edges. This observation clearly suggests that Ln increases with the degree of compensation. Chemical analyses (GDMS) realized on different regions of the wafer surface confirm this results, indicating a higher phosphorous concentration in the center than edges. (Actually this variation of concentration is due to the transport conditions of dopants in the liquid ahead of the crystallization front, which provokes phosphorous to segregate towards the center of the ingot, leading to an increase in the compensation level from the edges to the centre of the wafers.) These results show clearly the beneficial effect of compensation and allow understanding why the best solar cells are located near the inversion of polarity type.

Combining these results and numerical simulation, S. Dubois proposed a theoretical model suggesting that when carrier lifetime is limited by doping species, dopant compensation could be a convenient issue to increase solar cells performances [8].

#### References

- [1] A.F.B. Braga, et al., Sol. Energy Mater. Sol. Cells 92 (2007), pp. 418-424.

- [2] P. Woditsch et al., Sol. Energy Mater. Sol. Cells 72 (2002) pp. 11-26.

- [3] R. Einhaus et al., Proceedings of the 21<sup>st</sup> European PVSEC, Dresden, 2006, pp. 580-583.

- [4] J A. Waernes et al., 8<sup>th</sup> Silicon for the chemical industry Conference, Trondheim, 2006.

- [5] L. J. Geerligs et al., Proceedings of the 17<sup>th</sup> NREL Workshop, Colorado, 2007, pp. 169-173

[6] S. Dubois et al., Proceedings of the 23<sup>rd</sup> European PVSEC, Valencia, 2008, to be published.

- [7] R. Kvande et al., Proceedings of the 21<sup>st</sup> European PVSEC, Dresden, 2006, pp.1052-1056.

- [8] S. Dubois et al., Applied Physics Letters, 2008, to be published.

#### Dependency of Power Conversion Efficiency on Donor, Acceptor, and Blocking layer thickness for small-molecular Organic Solar Cell

Su-Hwan LEE, Dal-Ho KIM, Hee-Doo YANG, Ji-Hun KIM, Tae-Hun SHIM and Jea-Gun PARK\*

Nano SOI Process Laboratory, Hanyang University, Seoul 133-791, Korea

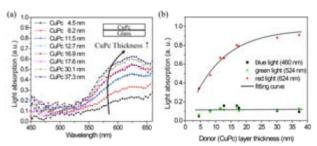

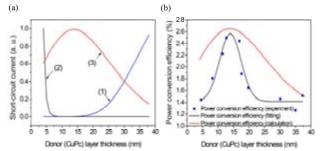

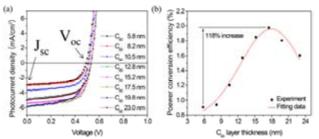

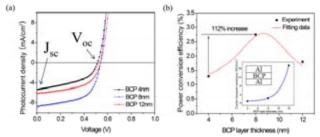

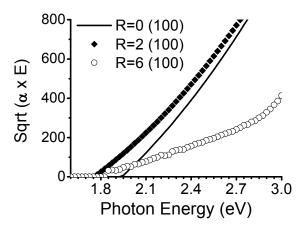

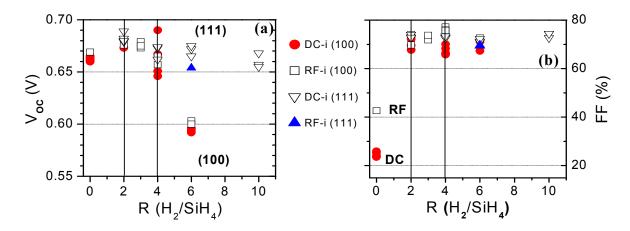

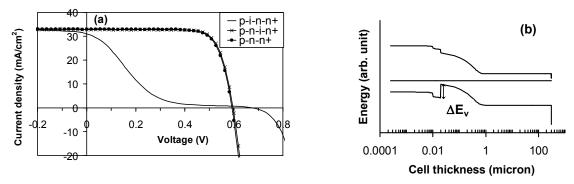

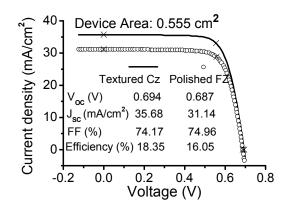

It has been reported that OPV device sandwiched with donor (CuPc), acceptor ( $C_{60}$ ), and hole/exciton blocking (BCP) layer between cathode and anode has been proposed a good device to obtain maximum power conversion efficiency [1-7]. However, they did not show how the power conversion efficiency is one another influenced by the thickness of organic donor (CuPc), acceptor ( $C_{60}$ ), and hole/exciton blocking (BCP) layer. In our study, thus, we investigated the impact of organic donor, acceptor, and hole/exciton blocking layer thickness on power conversion efficiency for small-molecular solar cell.

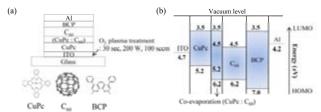

Fig. 1. Schematic structure and energy band diagram for the OPV device fabricated with a double small-molecular layer: (a) cross-sectional device structure and chemical structures, and (b) energy band diagram.

The OPV devices were fabricated with the following configuration by using a vacuum thermal evaporation: ITO glass substrate / CuPc (4.5, 8.2, 11.5, 12.7, 16.9, 17.6, 19.8, 30.1, 35, and 37.3 nm) / CuPc :  $C_{60}$  co-evaporation (interface layer; CuPc: $C_{60}$ =2.5:1, 11 nm) /  $C_{60}$  (5.8, 8.2, 10.5, 12.8, 15.2, 17.5, 19.8, and 23 nm) / BCP (4, 8, and 12 nm) / Al (100 nm). Figure 1 shows the schematic vertical structure, chemical structures of small-molecular materials, and the energy band diagram of the OPV device.

In order to investigate the power conversion efficiency depending on the donor (CuPc) layer thickness, the OPV device was fabricated with the sandwiched structure of variable thick donor layer, fixed thick interface layer (e.q., ~11.0 nm),  $C_{60}$  layer (e.q., ~17.5 nm), and BCP layer (e.q., ~8.0 nm).

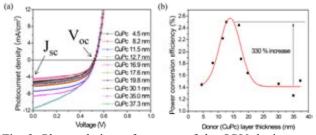

Fig. 2. Photovoltaic performance of the OPV device as a function of the CuPc layer thickness: (a) photocurrent density, and (b) power conversion efficiency.

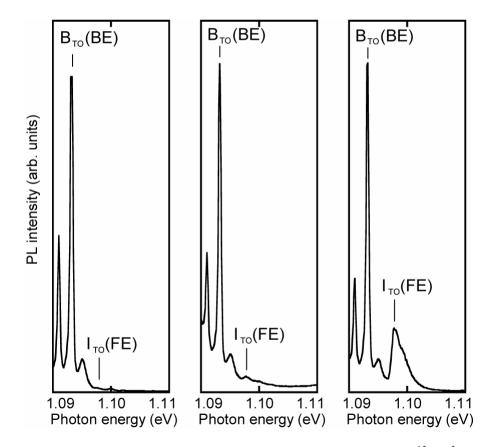

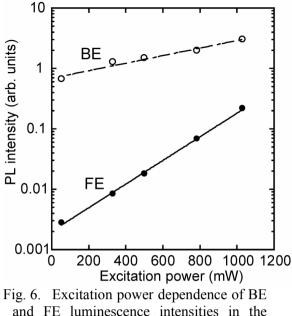

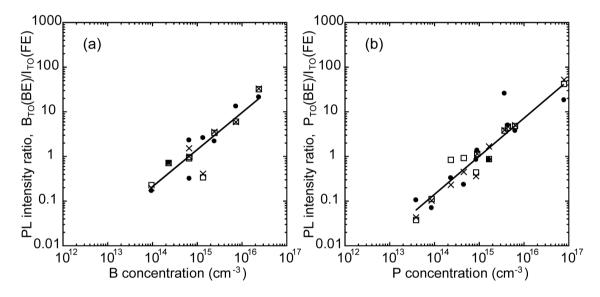

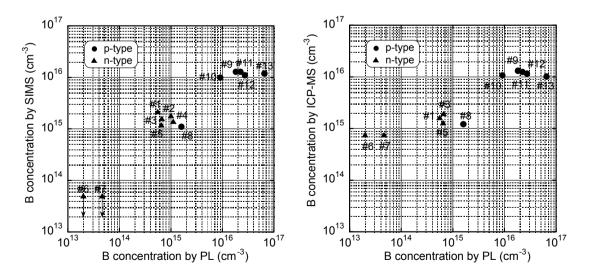

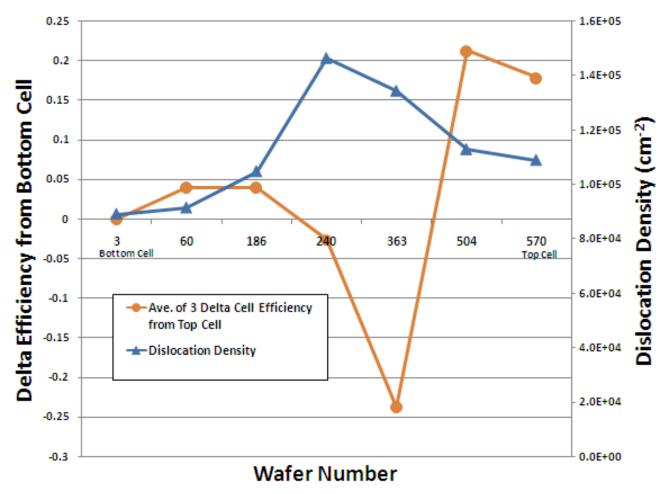

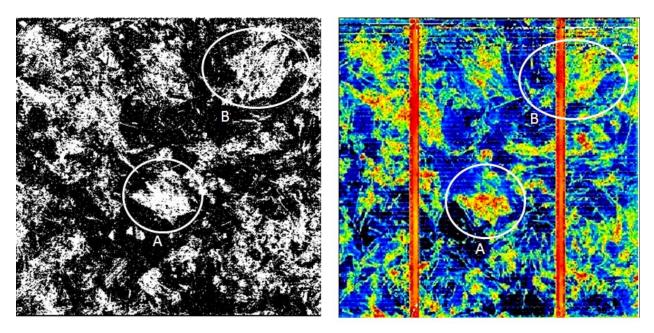

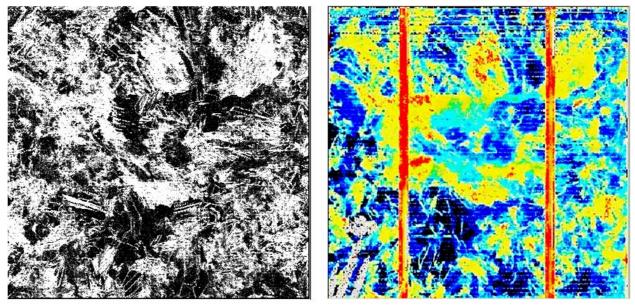

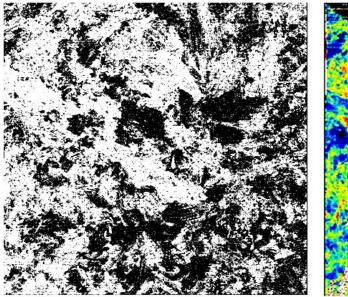

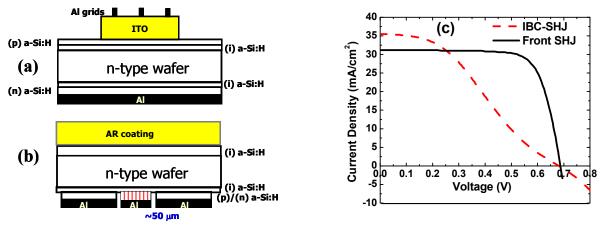

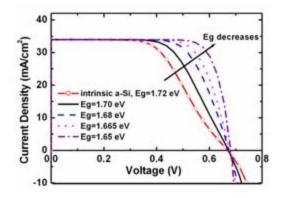

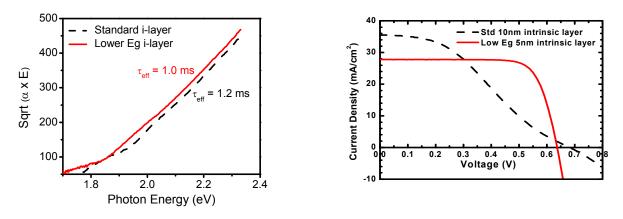

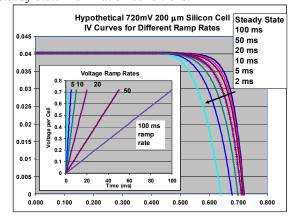

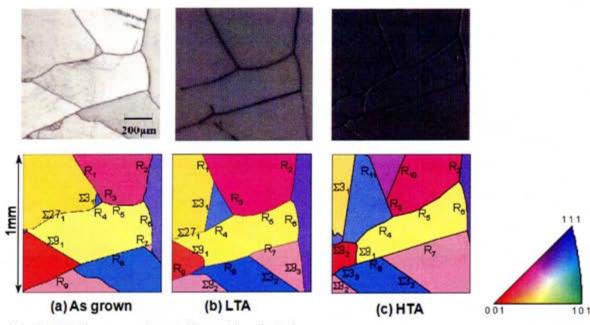

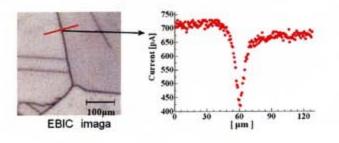

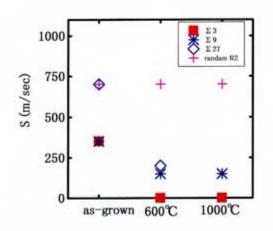

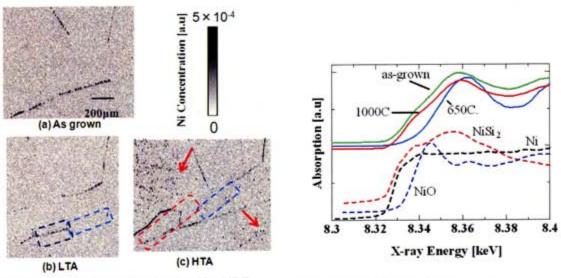

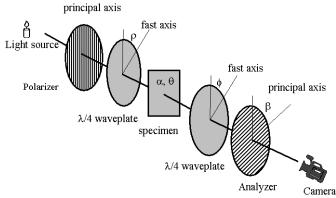

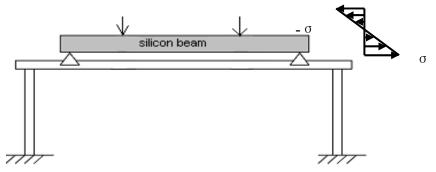

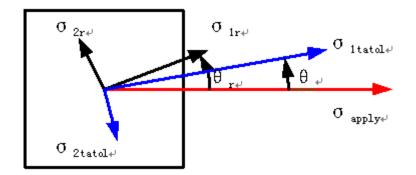

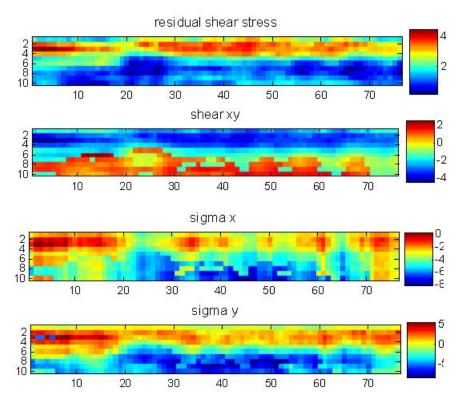

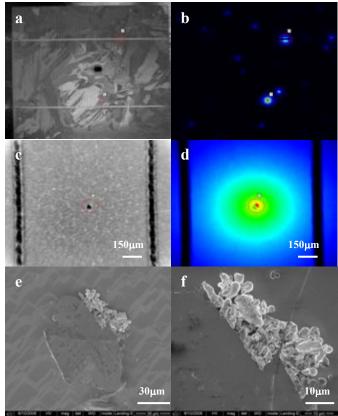

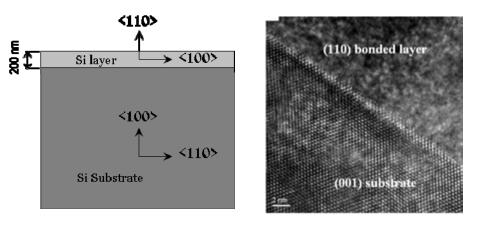

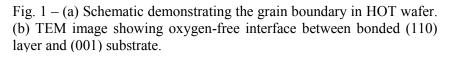

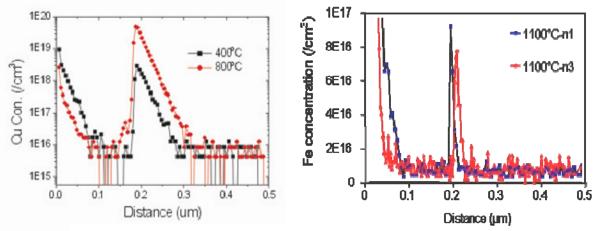

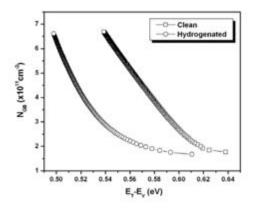

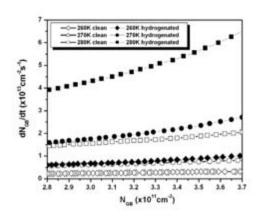

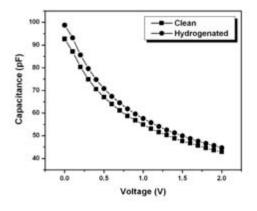

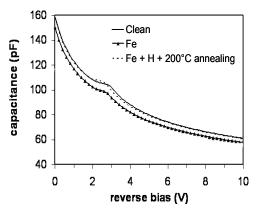

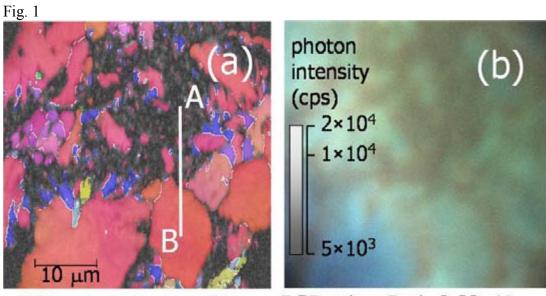

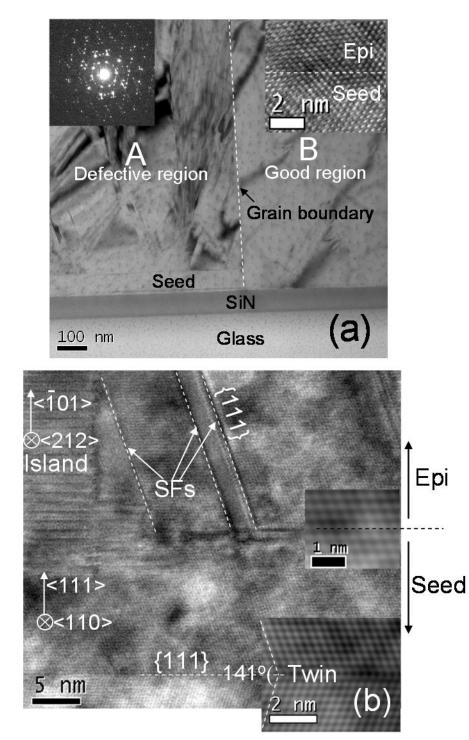

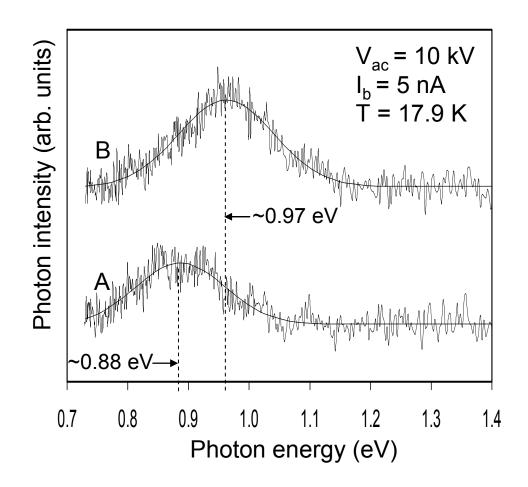

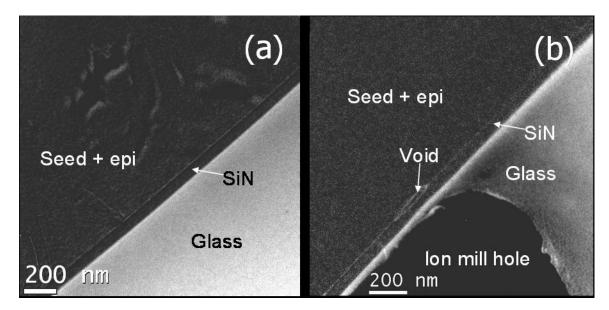

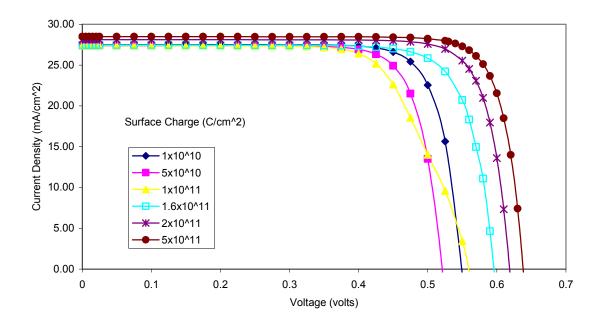

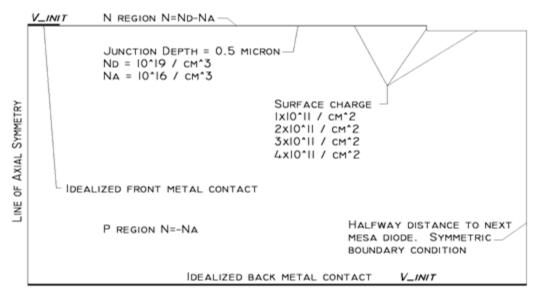

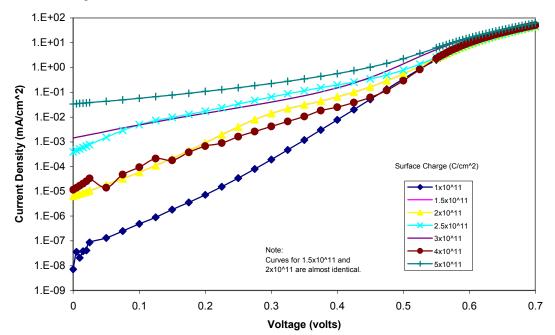

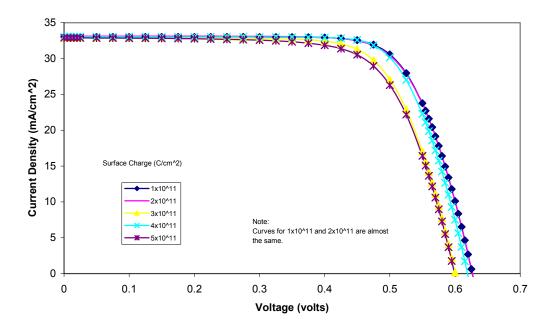

Figure 2 shows the characteristics of OPV device fabricated with double small-molecular layer as a function of CuPc layer thickness. Figure 2(a) shows the photocurrent density versus voltage (J-V) curves for the OPV device with a various CuPc layer thickness. The J<sub>sc</sub> was varied with the CuPc layer thickness while  $V_{\text{oc}}$  did not. The variation of  $V_{\text{oc}}$  was about 3.8% (from 0.515V to 0.535V).  $V_{oc}$  is determined by the energy gap between CuPc layer's highest occupied molecular orbital (HOMO) level and C<sub>60</sub> layer's lowest unoccupied molecular orbital (LUMO) level, Fig. 1(b). Although, the CuPc layer thickness is varied, the energy level between CuPc layer's HOMO level and C<sub>60</sub> layer's LUMO level is fixed. For this reason, the variation of  $V_{oc}$  is uniform. However, Jsc sharply increased with the CuPc layer thickness up to  $\sim 12.7$  nm and then suddenly decreased with increasing the CuPc layer thickness. Figure 2(b) shows the dependence of power conversion efficiency on the CuPc layer thickness. The power conversion efficiency was obtained under the illumination of 100 mW/cm<sup>2</sup>. The power conversion efficiency sharply increased with the CuPc layer thickness up to ~12.7 nm and then suddenly decreased with increasing the CuPc layer thickness. In comparison of Voc, Jsc, and power conversion efficiency, it is evident that the power